# **Mixed-Signal Blockset™**

User's Guide

# MATLAB&SIMULINK®

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

**T**

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Mixed-Signal Blockset™ User's Guide

© COPYRIGHT 2019-2022 by MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See <a href="https://www.mathworks.com/trademarks">www.mathworks.com/trademarks</a> for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

${\tt MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ {\tt www.mathworks.com/patents}\ for\ more\ information.}$

#### **Revision History**

| March 2019     | Online only | New for Version 1.0 (Release 2019a)     |

|----------------|-------------|-----------------------------------------|

| September 2019 | Online only | Revised for Version 1.1 (Release 2019b) |

| March 2020     | Online only | Revised for Version 1.2 (Release 2020a) |

| September 2020 | Online only | Revised for Version 1.3 (Release 2020b) |

| March 2021     | Online only | Revised for Version 2.0 (Release 2021a) |

| September 2021 | Online only | Revised for Version 2.1 (Release 2021b) |

| March 2022     | Online only | Revised for Version 2.2 (Release 2022a) |

| September 2022 | Online only | Revised for Version 2.3 (Release 2022b) |

# Contents

| PLL Featured Exam                                                         | ples |

|---------------------------------------------------------------------------|------|

| Phase Noise at PLL Output                                                 | 1-2  |

| PLL Design and Verification Using Data Sheet Specifications               | 1-13 |

| Tune Phase-Locked Loop Using Loop-Shaping Design                          | 1-23 |

| Digital Phase Locked Loop                                                 | 1-38 |

| Model PLLs in the Phase Domain                                            | 1-46 |

| DC Featured Exam                                                          | ples |

| Effect of Metastability Impairment in Flash ADC                           | 2-2  |

| Design and Evaluate Interleaved ADC                                       | 2-8  |

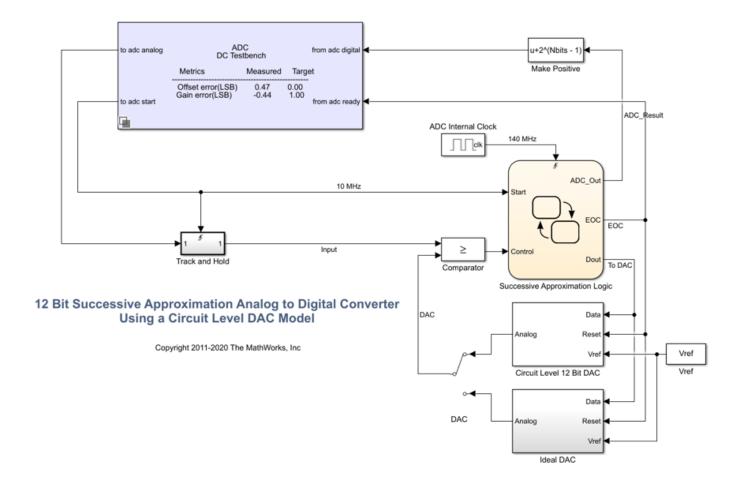

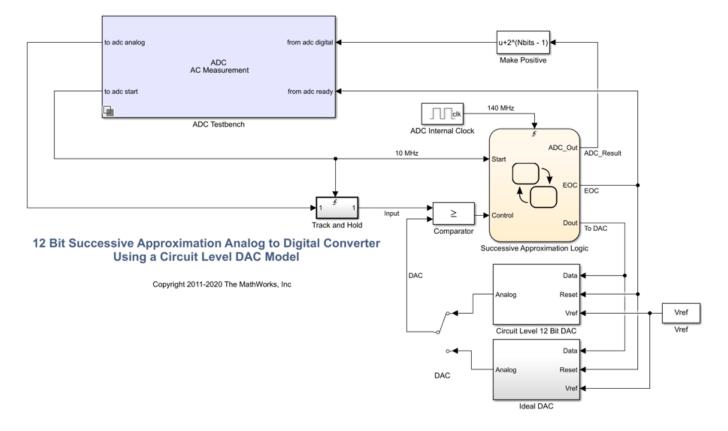

| Design and Evaluate Successive Approximation ADC Using Stateflow          | 2-19 |

| Analyzing Simple ADC with Impairments                                     | 2-27 |

| Subranging ADC                                                            | 2-35 |

| Measuring Offset and Gain Errors in ADC                                   | 2-44 |

| Compare SAR ADC to Ideal ADC                                              | 2-48 |

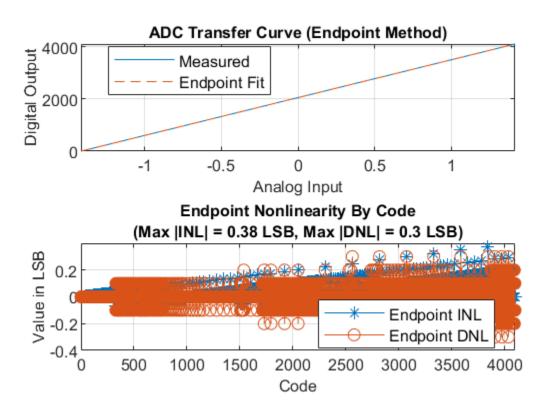

| ADC Linearity Measurement Using Histogram                                 | 2-52 |

| Oversampling Interpolating DAC                                            | 2-64 |

| Design and Evaluate Segmented DAC                                         | 2-73 |

| Compare Binary Weighted DAC to Ideal DAC                                  | 2-78 |

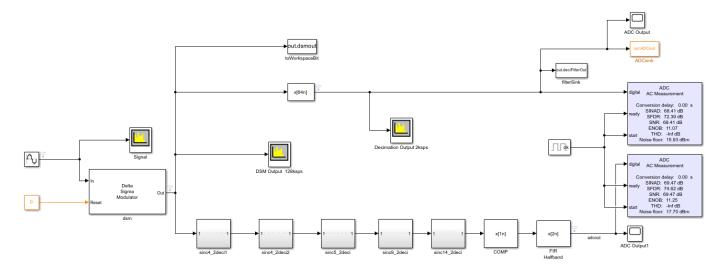

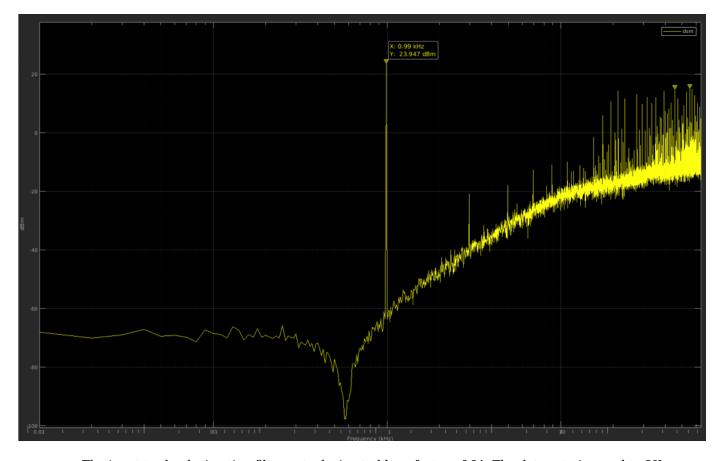

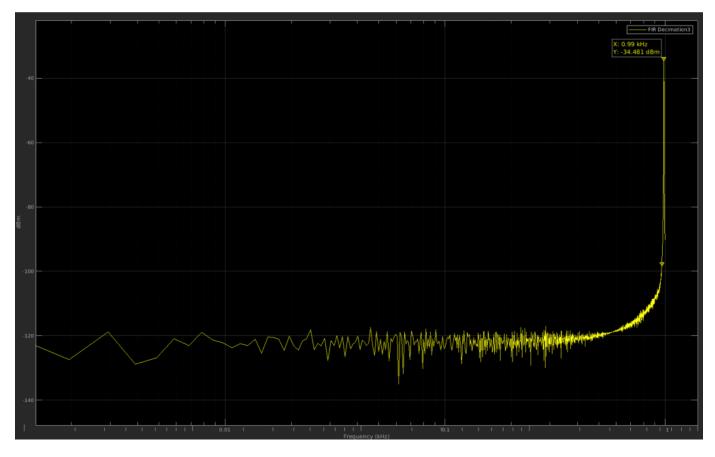

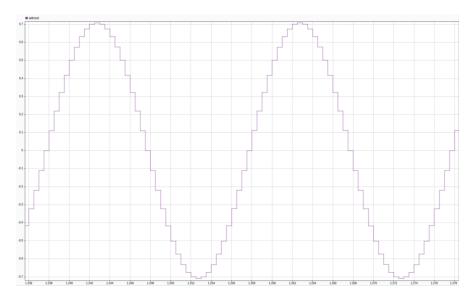

| Delta Sigma Modulator Data Converter with Half-Band Filter for Decimation | 2-81 |

| Mixing Analog and Digital Signals Featured Exam                      | ples         |

|----------------------------------------------------------------------|--------------|

|                                                                      |              |

| Digital Timing Using Solutions to Ordinary Differential Equations    | 3-2          |

| Digital Timing Using Fixed Step Sampling                             | 3-7          |

| Logic Timing Simulation                                              | 3-12         |

| Circuit Design Details Affect PLL Performance                        | 3-16         |

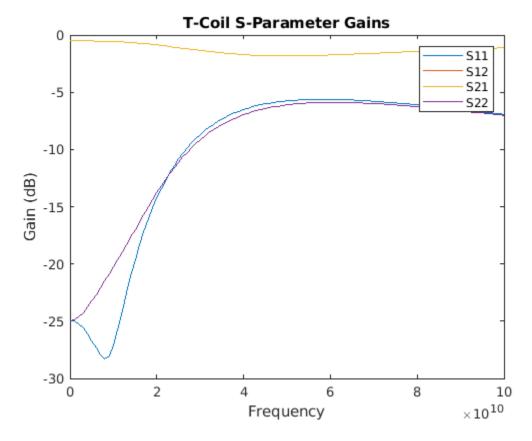

| Analyze T-Coil Circuit                                               | <b>3-3</b> 3 |

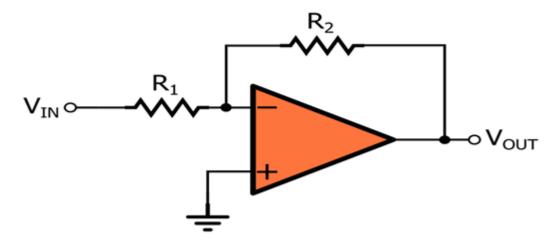

| Design Inverting Amplifier                                           | 3-42         |

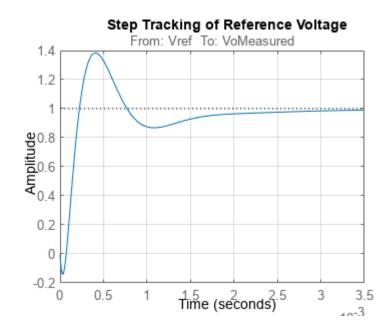

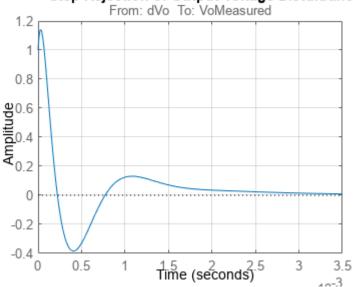

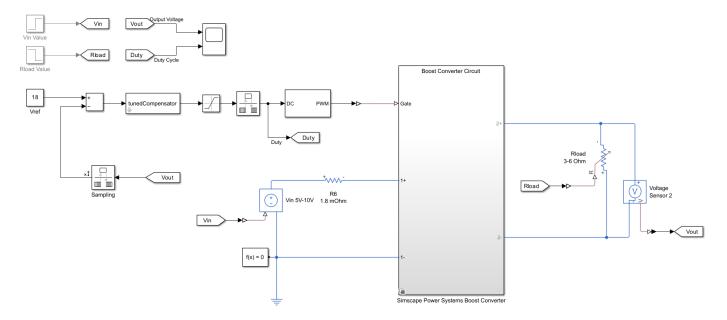

| Feedback Amplifier Design for Voltage-Mode Boost Converter           | 3-45         |

| PLL Block Level Exam                                                 | ples         |

| Measuring VCO Phase Noise to Compare with Target Profile             | 4-2          |

| Finding Voltage Sensitivity and Quiescent Frequency of VCO           | 4-4          |

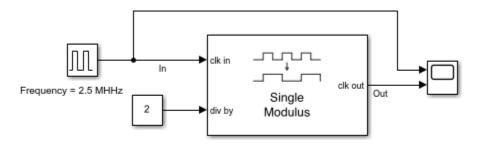

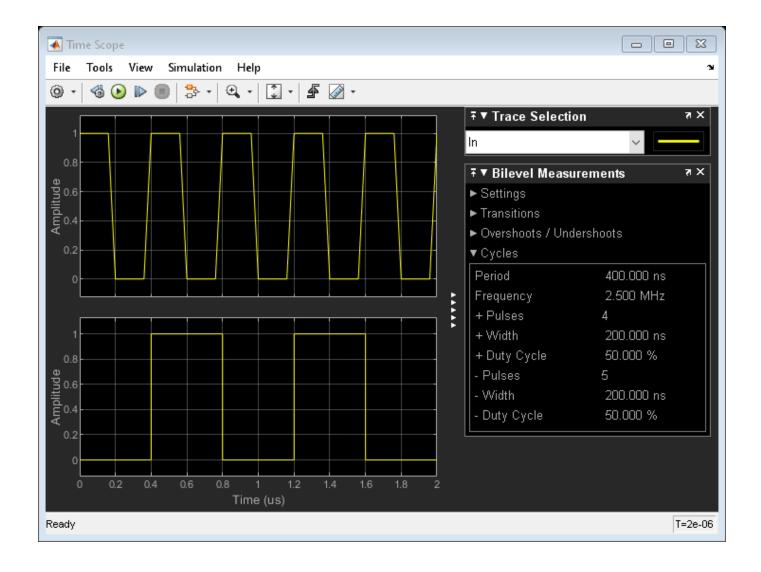

| Frequency Division Using Single Modulus Prescaler                    | 4-6          |

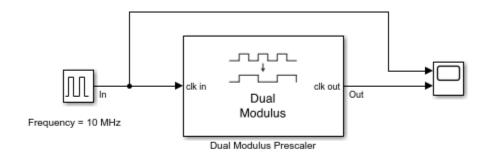

| Frequency Division Using Dual Modulus Prescaler                      | 4-8          |

| Frequency Division Using Fractional Clock Divider with Accumulator . | 4-10         |

| Frequency Division Using Fractional Clock Divider with DSM           | 4-12         |

| Data Converter Block Level Exam                                      | ples         |

| Measure Offset and Gain Error of Binary Weighted DAC                 | 5-2          |

| Measure AC Performance Metrics of Binary Weighted DAC                | <b>5-</b> 4  |

| Measure AC Performance Metrics of DAC Using DAC AC Measurement       | 5-6          |

| Measure DC Performance Metrics Using DAC DC Measurement              | 5-8          |

|            | Utilities Block Level Exam                          | pres       |

|------------|-----------------------------------------------------|------------|

| 6          |                                                     |            |

|            | Measure Timing Metrics of Periodic Signal           | 6-2        |

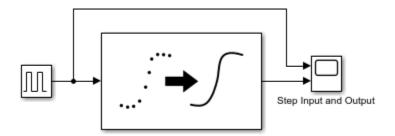

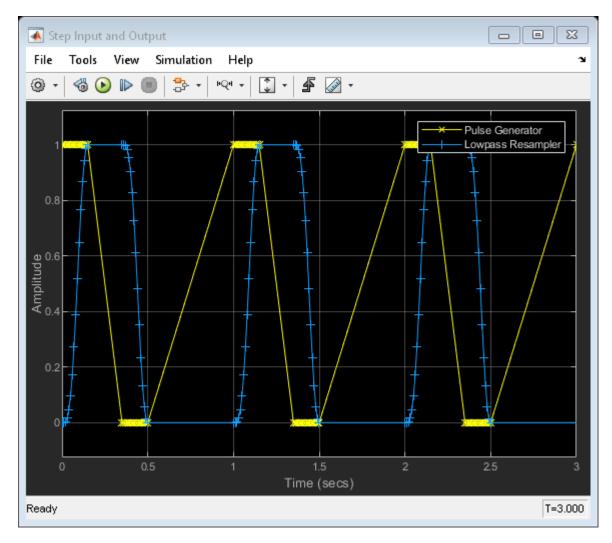

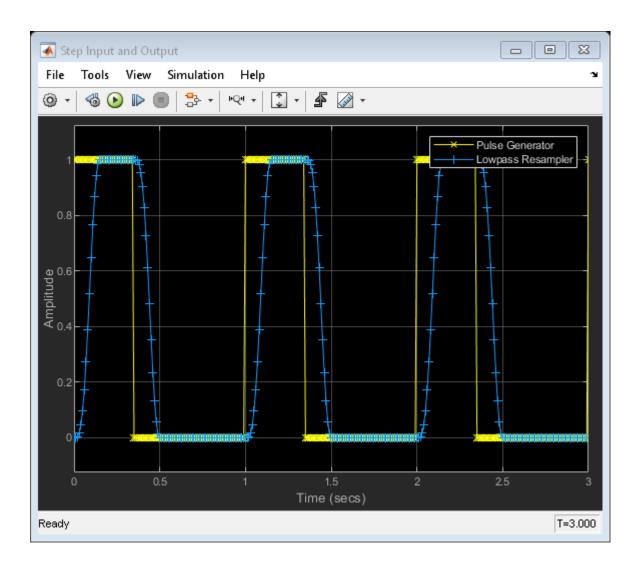

|            | Define Output Samples in Lowpass Resampler          | 6-3        |

| <b>7</b> [ | Mix Analog and Digital Sig                          | nals       |

| -          | Model Linear Circuit Response from SPICE Netlist    | 7-2        |

|            | Supported SPICE Syntax                              | 7-2<br>7-5 |

|            | Define Device Noise Using Linear Circuit Wizard     | 7-7        |

|            | Device List                                         | 7-7        |

|            | Device Noise Specification                          | 7-7        |

|            | Ports Supported in Linear Circuit Wizard            | 7-9        |

|            | Block Ports                                         | 7-9        |

|            | Parameter Dialog                                    | 7-9        |

|            | Port Report                                         | 7-10       |

|            | MATLAB Systems Generated from Linear Circuit Wizard | 7-11       |

|            | Verify MATLAB System Block Configuration            | 7-11       |

|            | Build MATLAB System Block                           | 7-11       |

|            | Sample Time                                         | 7-11       |

# **PLL Featured Examples**

- "Phase Noise at PLL Output" on page 1-2

- "PLL Design and Verification Using Data Sheet Specifications" on page 1-13

- "Tune Phase-Locked Loop Using Loop-Shaping Design" on page 1-23

- "Digital Phase Locked Loop" on page 1-38

- "Model PLLs in the Phase Domain" on page 1-46

### **Phase Noise at PLL Output**

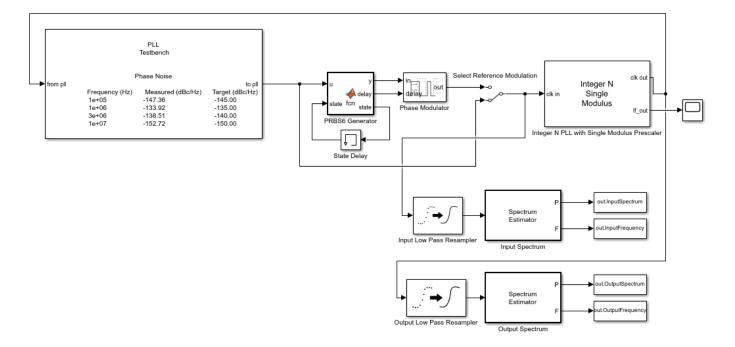

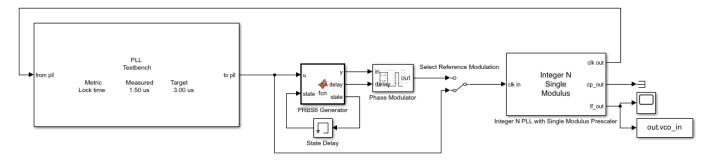

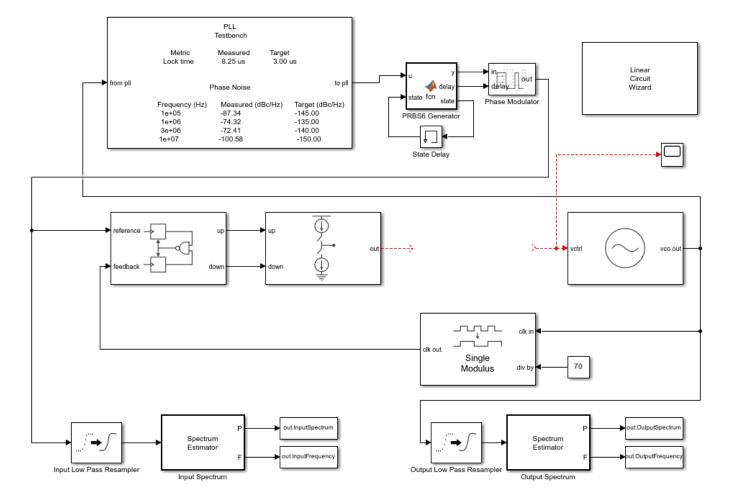

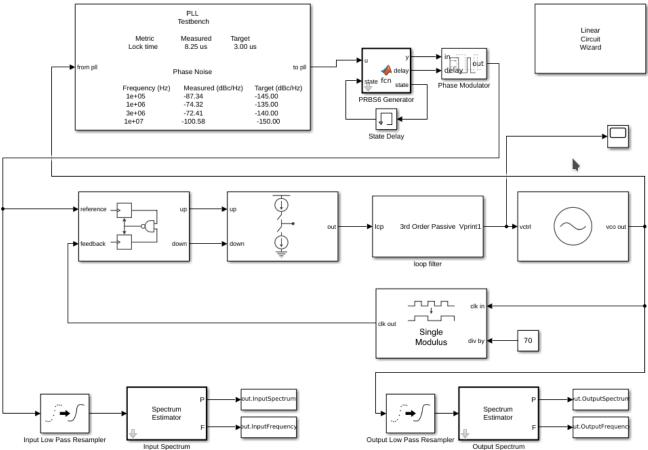

This example shows how to predict the phase noise at the output of a phase-locked loop (PLL), simulate the PLL using the PLL Testbench, and compare the simulation results to theoretical predictions.

This example demonstrates three phase noise effects, individually or combined, depending on the configuration you choose:

- 1 Reference modulation or phase noise

- 2 VCO phase noise

- **3** VCO phase noise subsampled by the feedback prescaler

Open the model PllPhaseNoiseExample.slx.

open\_system('PllPhaseNoiseExample.slx');

This example uses an Integer N PLL with Single Modulus Prescaler from the Mixed Signal Blockset™.

The PLL Testbench generates the reference input signal for the PLL and measures the phase spectral density at the output of the PLL.

The optional PRBS6 reference phase modulation in this model is used to contrast the response to reference phase variation with the response to VCO phase noise.

The low pass resamplers at the inputs to the spectrum estimators are anti-aliasing filters. These filters convert the variable step discrete signals to the fixed step discrete signals required by the spectrum estimators.

The spectra of the PLL input and output signals are estimated and logged in the base workspace so that you can compare the simulation results to the results of the theoretical calculations.

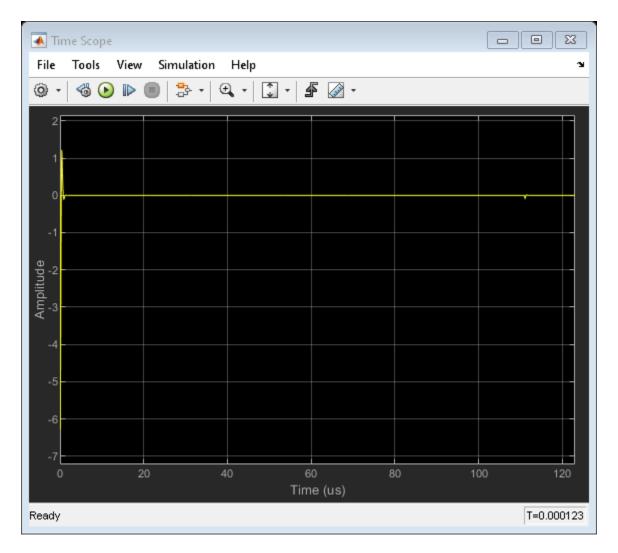

The oscilloscope in the example model provides a progress indicator for the simulation.

To evaluate the behavior of the PLL under a variety of conditions, use a separate workspace file for each different set of conditions. This example provides five such supporting .mat files. All of them produce the same loop transient response.

- Baseline.mat As close to ideal as possible. Use to evaluate numerical noise introduced by the model and simulator.

- **2** ReferenceModulation.mat Introduce reference phase modulation. Use to evaluate the phase transfer function of the PLL.

- **3** VCOPhaseNoise.mat Introduce VCO phase noise and a prescaler ratio equal to one. Use to evaluate the PLL control loop's error function.

- 4 InbandPhaseNoise.mat Introduce VCO phase noise and a prescaler ratio greater than one. Use to evaluate the effect of the prescaler ratio on the PLL control loop's error function.

- **5** TotalPhaseNoise.mat All phase noise sources are enabled, and the prescaler ratio is greater than one.

#### **Theoretical Calculations**

This section shows how to calculate the expected response of the PLL.

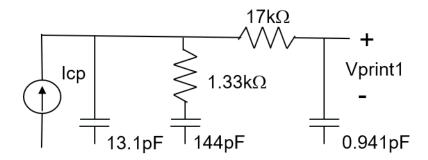

The target loop bandwidth of the PLL is 2 MHz with a 45 degree phase margin. The loop filter components are scaled to practical level and the charge pump output current is scaled by the same factor to maintain the same loop dynamics.

The function getPllLoopResponse calculates the loop gain as a function of frequency and then calculates the expected response to signals from outside or inside the PLL. Define the input parameters such as charge pump output current, VCO sensitivity, prescaler ratio and passive loop filter component values for the getPllLoopResponse function to use.

```

PllKphi = 5e-3;

% Charge Pump output current

PllKvco = 100e6;

% VCO sensitivity

PllN

% Prescaler ratio

= 70;

PllR2

= 1.33e3;

% Loop filter resistance for second order response (ohms)

PllR3

= 1.7e4;

% Loop filter resistance for third order response (ohms)

% Loop filter resistance for fourth order response (ohms)

PllR4

= 0;

= 1.31e-11; % Loop filter direct capacitance (F)

PllC1

= 1.44e-10; % Loop filter capacitance for second order response (F)

PllC2

= 9.41e-13; % Loop filter capacitance for third order response (F)

PllC3

PllC4

% Loop filter capacitance for fourth order response (F)

```

The script prepareExpectedSpectra computes the spectral density of the reference phase modulation and the VCO output phase noise. The script then also combines the result with the PLL loop response to obtain the phase noise spectral density at the output of the PLL. The reference phase modulation is a deterministic process for which the amplitude of the spectral components is expressed as a fraction of the carrier amplitude (dBc). In contrast, the VCO phase noise is a stochastic process for which the spectral density is expressed in dBc/Hz.

Define the input parameters for the prepareExpectedSpectra script such as reference input frequency, number of reference cycles per symbol of PRBS6 phase modulation data pattern, amplitude of a single spectral component of the PRBS6 reference phase modulation, resolution

bandwidth to evaluate spectra with phase noise, frequency offset vector, and phase noise spectral densities at specified frequency offset.

```

PllAddPhaseNoise = 'on'; % Enable VCO phase noise

PllFoffset

= [30e3 100e3 1e6 3e6 10e6]; % VCO offset frequencies (Hz)

PllPhaseNoise = [-56 - 106 - 132 - 143 - 152]; % VCO output phase noise (dBc/Hz)

CfgSelectRefMod = '0'; % Enable reference phase noise modulation

CfgRef = 30e6;

% Reference frequency

CfgCyclesPerSymbol = 2; % Reference cycles per PRBS6 modulation symbol

= -110;

CfgModLevel

% Reference phase modulation level (dBc/Hz)

CfgResBandwidth = 100e3; % PLL Testbench resolution bandwidth

CfgTargetSpectrum = [100e3 -145; 1e6 -135; 3e6 -140; 10e6 -150];

% PLL Testbench target phase noise (dBc/Hz)

```

If the variable WorkspaceFile exists and points to a file that can be loaded, load that file into the workspace. To use a configuration supplied with this example, set the value of WorkspaceFile to the name of the file for that configuration.

```

if exist('WorkspaceFile','var') && exist(WorkspaceFile,'file')

load(WorkspaceFile);

end

```

Analyze the PLL control loop using the getPllLoopResponse function. The outputs of this function are:

- LoopFrequency The frequency points at which the expected responses is calculated.

- LoopZofs The transfer impedance of the loop filter as a function of the frequency.

- LoopGofs The loop gain from the output of the prescaler to the input of the VCO, including the VCO voltage sensitivity. Note that the prescaler ratio is not included in this output, but is included in the closed loop transfer functions.

- LoopHofs The closed loop phase transfer function fromt the PLL reference input to the PLL output.

- LoopEofs The closed loop phase error transfer function with respect to the VCO output.

```

[LoopFrequency, LoopZofs, LoopGofs, LoopHofs, LoopEofs, LoopPhStep] = ...

getPllLoopResponse([0,PllR2,PllR3,PllR4],[PllC1,PllC2,PllC3,PllC4], ...

PllKphi, PllKvco, PllN);

```

Organize the computation of expected spectral density to place spectral components directly into the frequency bins.

The workspace variables for the expected spectral density are:

- ExpInputFrequency A vector of frequencies for which the expected input spectrum is calculated (Hz).

- ExpInputSpectrum A vector of expected spectrum values at the reference input to the PLL (dBm into a one ohm load at a resolution bandwidth of CfgResBandwidth).

- ExpOutputFrequency A vector of frequencies for which the expected output spectrum is calculated (Hz).

- ExpOutputSpectrum A vector of expected spectrum values at the PLL output (dBm into a one ohm load at a resolution bandwidth of CfgResBandwidth).

prepareExpectedSpectra;

#### **Examine Expected Results**

In this section, examine the expected PLL behavior.

Start by looking at the closed loop response of the PLL. Consider three fundamental responses: transient response, transfer function, and error function.

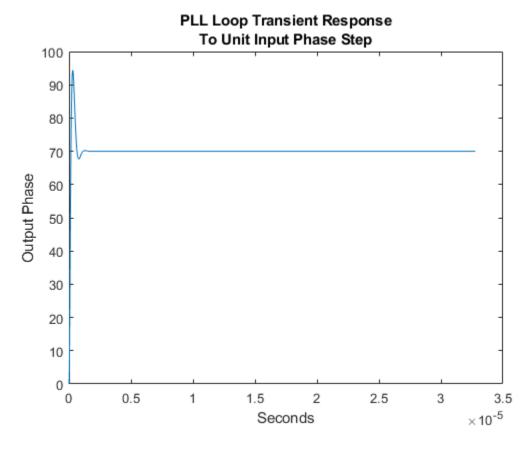

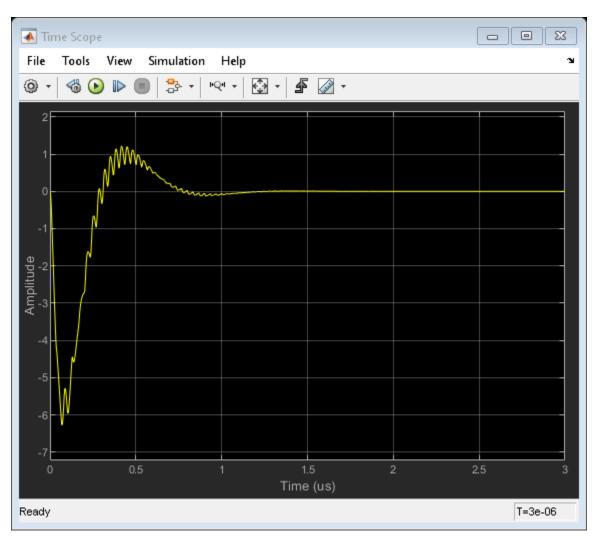

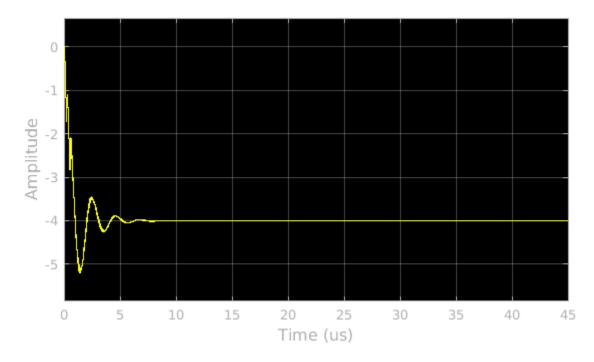

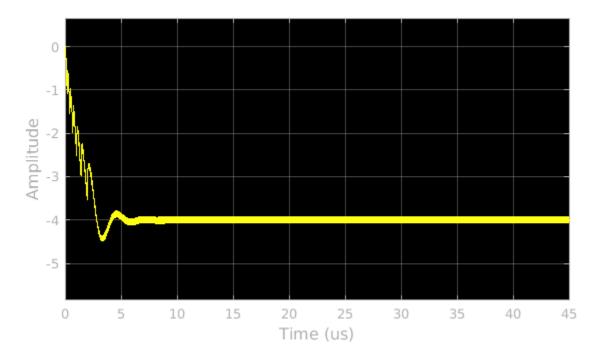

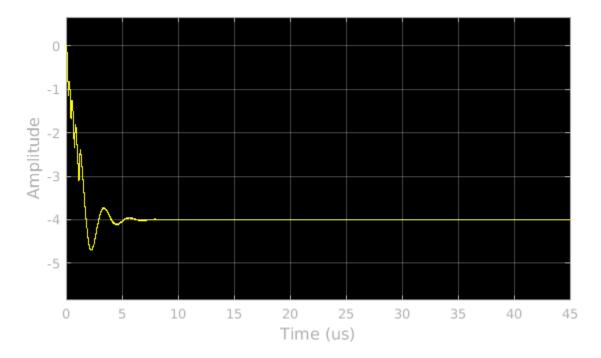

#### **Transient response**

In most PLL applications, the loop transient response is most important when the loop is initially acquiring phase lock. For very small initial frequency offsets or for relatively high closed loop bandwidth, the transient response predicts the loop acquisition time reasonably accurately. However, in many cases, the loop transient response only represents the response during phase acquisition, after frequency acquisition has already occurred. This example only addresses the phase acquisition time.

Plot the loop transient response of the PLL.

```

figure(1);

plot(LoopPhStep.Time,LoopPhStep.Data);

title({'PLL Loop Transient Response';'To Unit Input Phase Step'});

xlabel('Seconds');

ylabel('Output Phase');

```

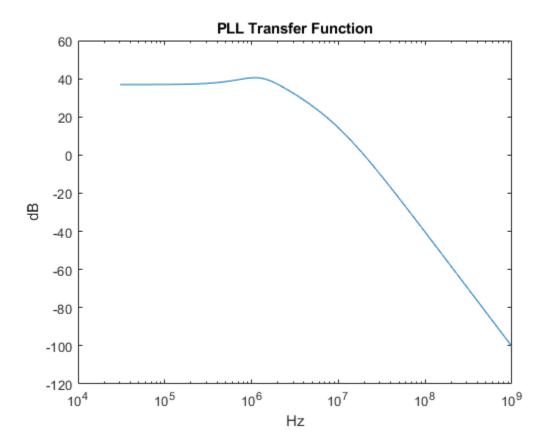

Transfer function

The transfer function from the reference input to the PLL output can be important either when the PLL is expected to track a modulated input very accurately or when it is expected to filter out noise from a noisy input.

Create a log-log plot of the PLL transfer function.

```

figure(2);

semilogx(LoopFrequency,20*log10(abs(LoopHofs)));

title('PLL Transfer Function');

xlabel('Hz');

ylabel('dB');

```

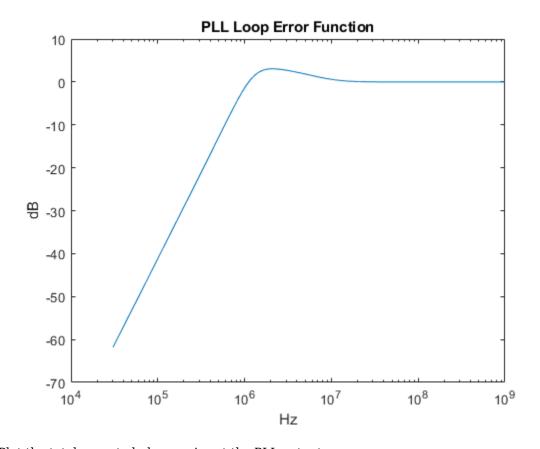

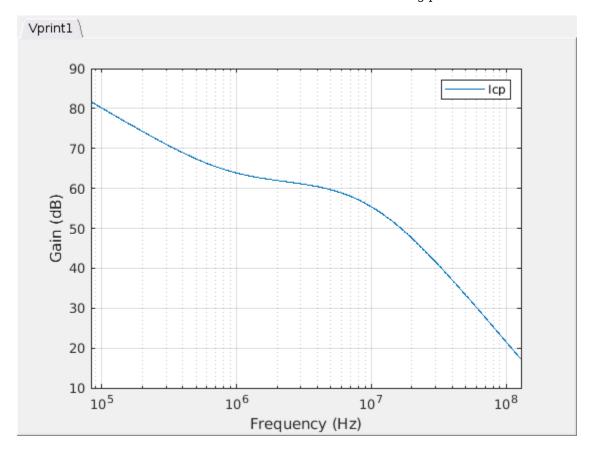

#### **Error function**

The PLL control loop is expected to reject phase noise generated inside the PLL itself, such as VCO phase noise. The transfer function between the VCO phase noise and the PLL output is sometimes called the loop error function. Examining this transfer function helps compensate the loop error before it is applied to another noise source.

Create a log-log plot of the PLL loop error function.

```

figure(3);

semilogx(LoopFrequency,20*log10(abs(LoopEofs)));

title('PLL Loop Error Function');

xlabel('Hz');

ylabel('dB');

```

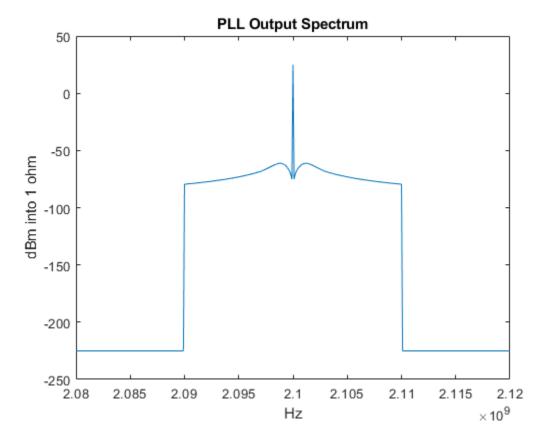

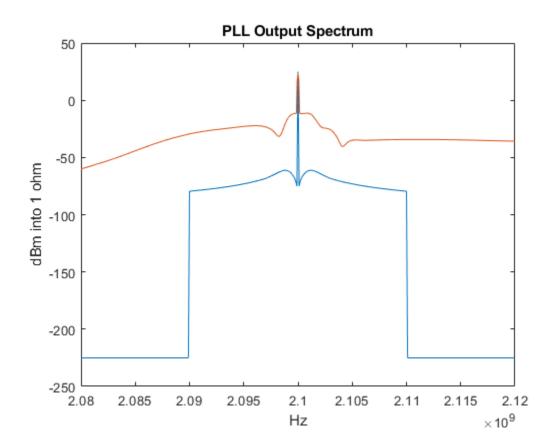

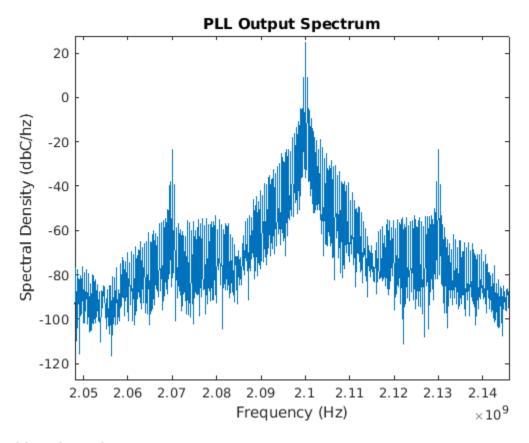

Plot the total expected phase noise at the PLL output.

```

figure(4);

plot(ExpOutputFrequency,ExpOutputSpectrum);

title('PLL Output Spectrum');

xlabel('Hz');

ylabel('dBm into 1 ohm');

xlim([PllN*CfgRef-2*PllFoffset(end), PllN*CfgRef+2*PllFoffset(end)]);

```

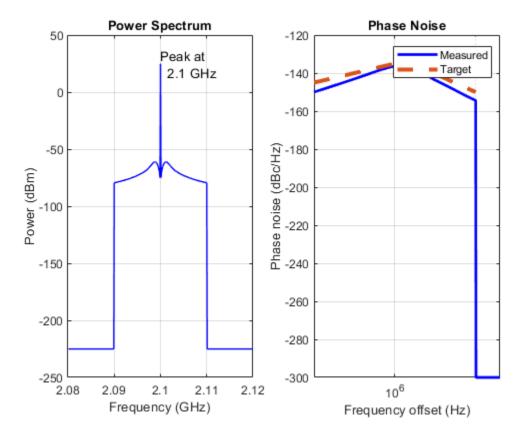

The phaseNoiseMeasure function is a callback function used by the PLL Testbench. It displays the target output phase noise spectral density along with the simulated or expected phase noise spectral density.

To compare the expected output phase noise to a specific design target, define the workspace variable CfgTargetSpectrum. CfgTargetSpectrum consists of two column arrays that specify the target phase noise at the output of the PLL. The first column specifies the frequency offsets in Hz and the second column specifies the corresponding phase noise spectral density if dBc/Hz. The PLL Testbench uses the callback function phaseNoiseMeasure to display the expected and simulated phase noise spectral density.

View the expected PLL output phase noise in units of dBc/Hz.

```

[~] = phaseNoiseMeasure(ExpOutputFrequency,ExpOutputSpectrum,...

CfgResBandwidth, CfgTargetSpectrum(:,1).','on','5', ...

CfgTargetSpectrum(:,2).');

```

If the loop response is not satisfactory, you might look at more detailed results such as the loop filter transimpedance (LoopZofs) to get additional insights that could help you improve the PLL design.

#### **Run the Simulation**

While the configuration process is straightforward, there are many parameters to be configured. Use the configureExamplePLL script to configure the PLL Simulink® model, then execute the model.

```

configureExamplePll;

SimOut = sim('PllPhaseNoiseExample');

```

To make the plotting easier, transform the results into the following four workspace variables:

- SimInputFrequency A vector of frequencies for which the input spectrum of the simulation is stored (Hz).

- SimInputSpectrum A vector of spectrum values at the reference input to the PLL (dBm into a one ohm load at a resolution bandwidth of CfgResBandwidth).

- SimOutputFrequency A vector of frequencies for which the output spectrum of the simulation is calculated (Hz).

- SimOutputSpectrum A vector of simulated spectrum values at the PLL output (dBm into a one ohm load at a resolution bandwidth of CfgResBandwidth).

Make the results easier to plot from the workspace.

```

SimInputFrequency = reshape(SimOut.InputFrequency.Data(:,end),1,[]);

SimInputSpectrum = reshape(SimOut.InputSpectrum.Data(:,end),1,[]);

SimOutputFrequency = reshape(SimOut.OutputFrequency.Data(:,end),1,[]);

SimOutputSpectrum = reshape(SimOut.OutputSpectrum.Data(:,end),1,[]);

```

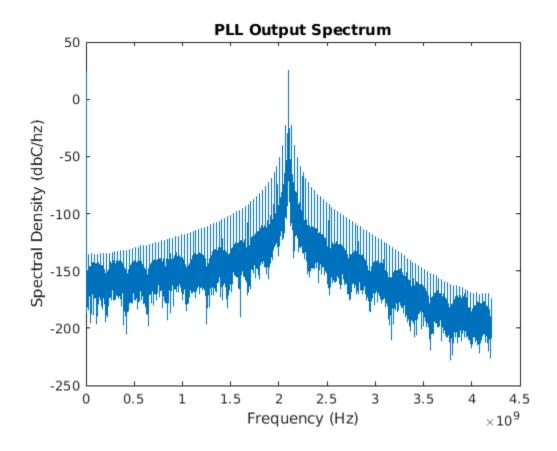

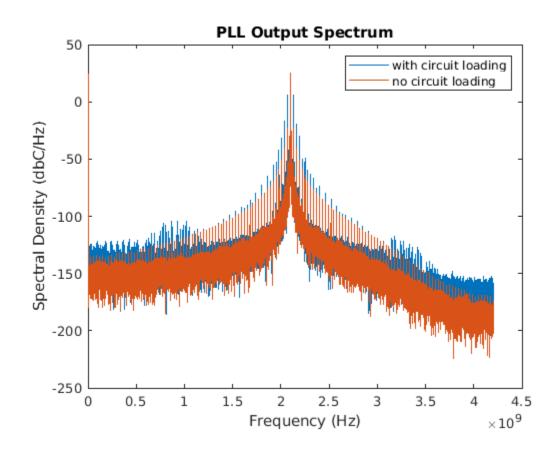

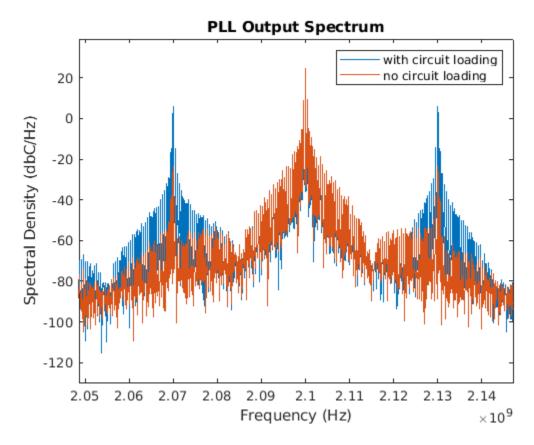

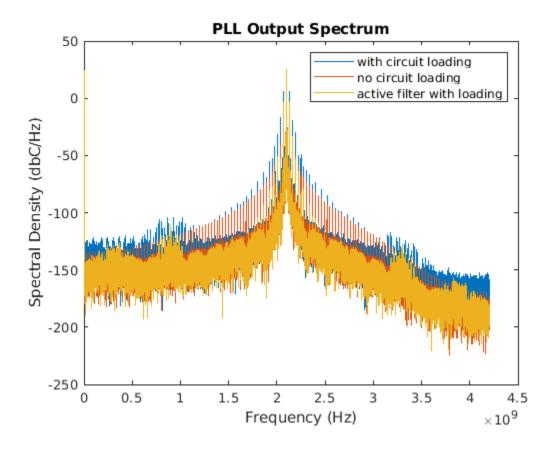

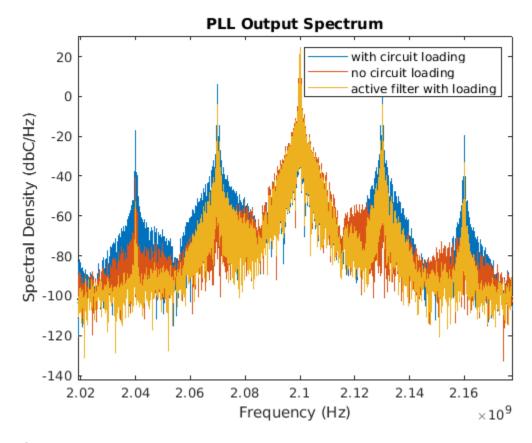

#### **Compare Expected and Simulated Results**

Compare expected and simulated phase noise at the PLL output.

```

figure(4);

plot(ExpOutputFrequency,ExpOutputSpectrum);

title('PLL Output Spectrum');

xlabel('Hz');

ylabel('dBm into 1 ohm');

xlim([PllN*CfgRef-2*PllFoffset(end), PllN*CfgRef+2*PllFoffset(end)]);

hold on;

plot(SimOutputFrequency,SimOutputSpectrum);

hold off;

```

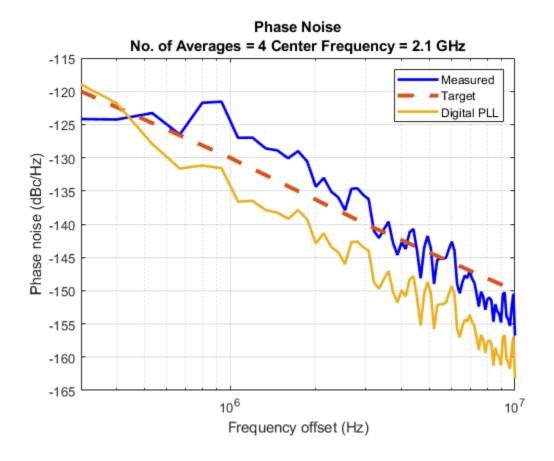

View the expected PLL output phase noise in units of dBc/Hz.

```

[~] = phaseNoiseMeasure(SimOutputFrequency,SimOutputSpectrum,...

SimOutputFrequency(2)-SimOutputFrequency(1),...

CfgTargetSpectrum(:,1).','on','5',CfgTargetSpectrum(:,2).');

```

#### **Save the Configuration and Results**

Save the entire workspace, including the system configuration in its current state and the results, to a file. If the WorkspaceFile variable already exists, you can resave the current state to that file. To save to a new file, change the value of WorkspaceFile.

```

if exist('WorkspaceFile','var')

save(WorkspaceFile);

end

```

#### **See Also**

Integer N PLL with Single Modulus Prescaler | PLL Testbench | Variable Pulse Delay

#### **More About**

• "PLL Design and Verification Using Data Sheet Specifications" on page 1-13

# PLL Design and Verification Using Data Sheet Specifications

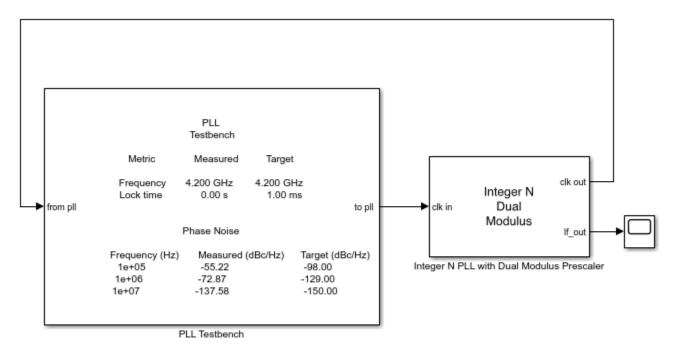

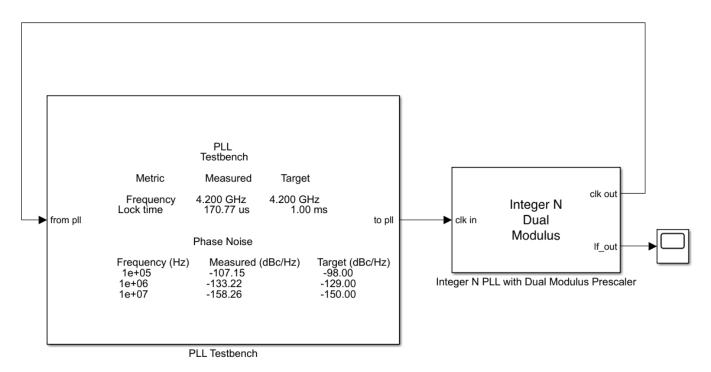

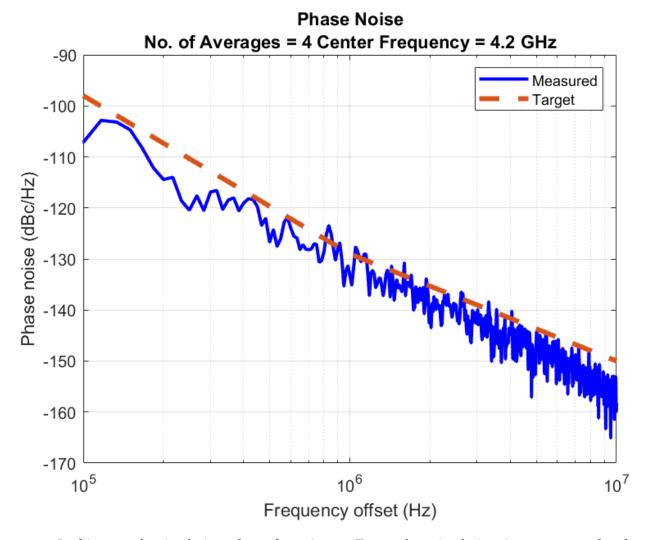

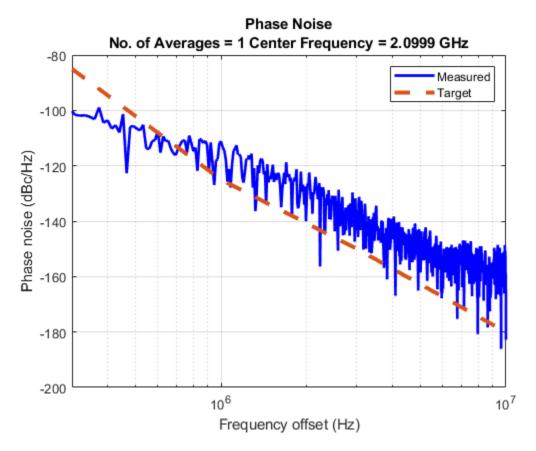

This example shows how to use Mixed-Signal Blockset<sup>™</sup> to model a commercial off-the-shelf integer-N phase-locked loop (PLL) with dual modulus prescaler operating around 4 GHz. You can verify the PLL performance, including phase noise.

You can use PLL models to explore and design different loop filters, simulate different operating frequencies, determine different divider ratios, or assess the frequency synthesizer performance once embedded in a larger system. For example, Mixed-Signal Blockset PLL models can be helpful if you need to integrate a PLL into a System on Chip or a System on Board.

For this example, use the data sheet of Skyworks SKY73134-11. This is a wideband PLL Frequency Synthesizer operating between 350 MHz and 6.2 GHz.

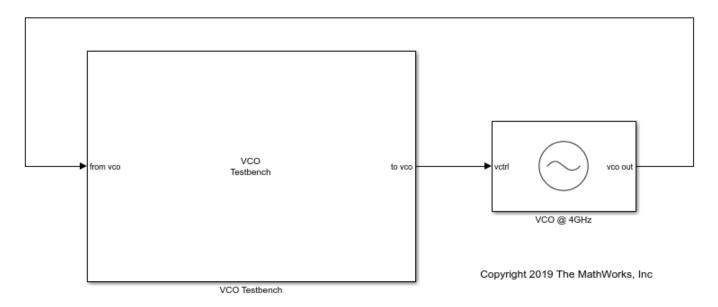

#### **Build VCO Model**

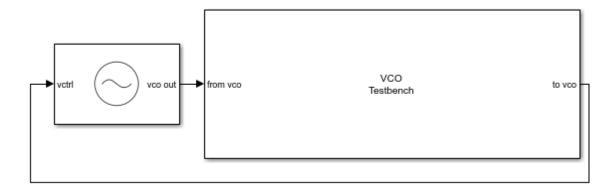

Open the model VCO\_model, which has VCO and VCO Testbench blocks from Mixed-Signal Blockset connected together.

```

model = 'VCO_model';

open system(model);

```

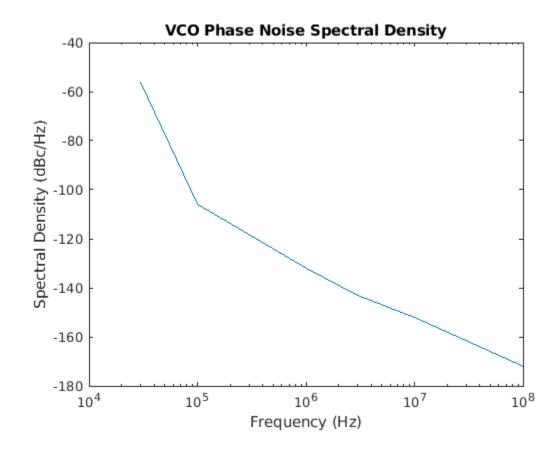

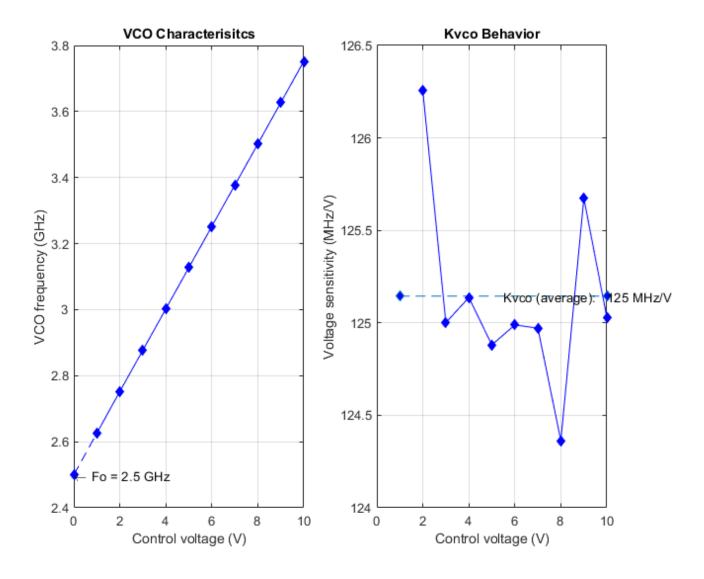

Inspect the data sheet to identify the characteristics of the voltage controlled oscillator (VCO). VCO is the main component contributing to the phase noise of the PLL. Table 6 of the data sheet lists the typical VCO sensitivity (*Kvco*) as 20 MHz/V. Set the **Voltage Sensitivity** of the VCO block to 20e6 Hz/V. The data sheet does not provide the free running frequency (*Fo*) of the VCO, so you can set it to an arbitrary value close to the operting frequency. In this case, set **Free running frequency** to 3.9e9 Hz.

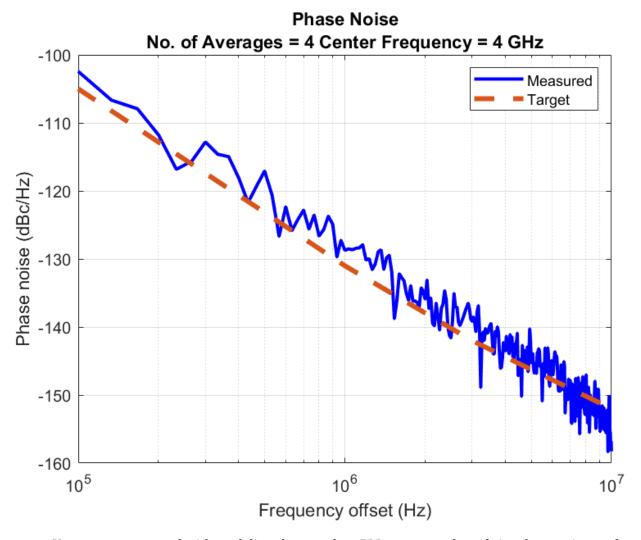

For this example, simulate the PLL behavior when the PLL locks around 4 GHz. Table 7 of the data sheet lists the VCO phase noise profile as: around 4 GHz is,

- −105 dBc/Hz at 100 kHz

- -131 dBc/Hz at 1 MHz

- -142 dBc/Hz at 3 MHz

- -152 dBc/Hz at 10 MHz

Use the phase noise profile to add phase noise impairment to the VCO. To speed up simulation, ignore the phase noise data points at lower frequency offsets. Simulation takes longer to capture the phase noise profile close to the carrier.

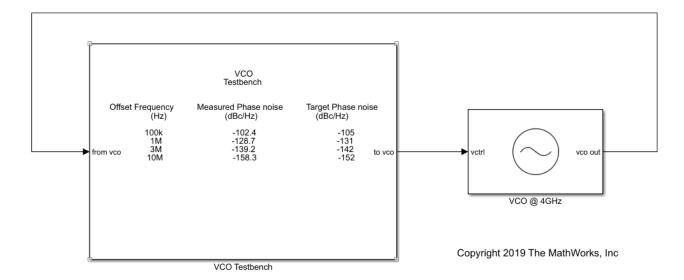

#### **Measure VCO Phase Noise**

The testbench provides the control voltage (*Vctrl*) stimulus to the VCO and measures the VCO phase noise. The output frequency (*F*) of the VCO is :

$$F = Kvco * Vctrl + Fo$$

Substituting the values for the output frequency, the free running frequency, and the voltage sensitivity, the equation gives a control voltage of be 5 V.

Click on **Autofill setup parameters** and **Autofill target metric** buttons to automatically populate the measurement parameters for both setup and target metric. The target metric provides the anticipated phase noise profile for comparison with the simulation results. The testbench setup properties define the signal sampling frequency and the measurement resolution bandwidth.

To speed up simulation time, reduce **No. of spectral averages** to 4.

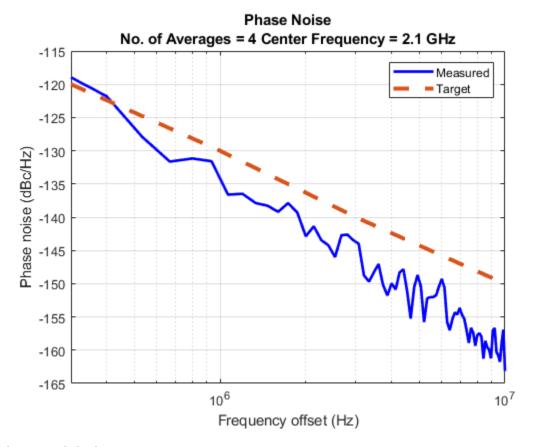

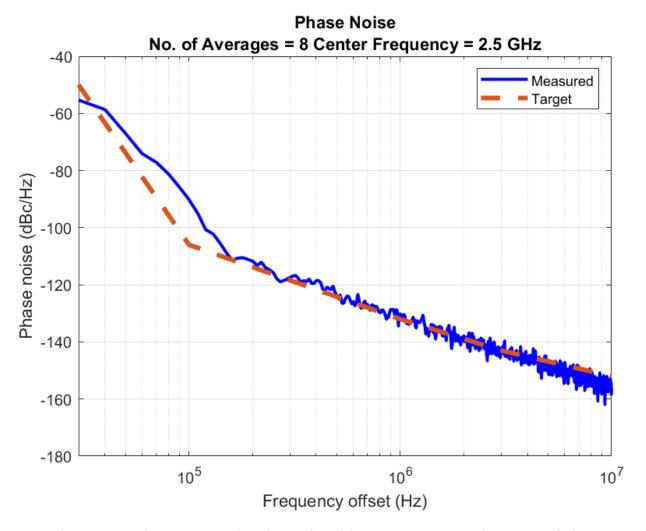

Run the simulation. Verify that the VCO model reproduces the phase noise profile specified in the target metric.

You can now proceed with modeling the complete PLL system and verify its phase noise performance.

#### **Build PLL Model**

From the **Features** section of the data sheet, see that this PLL is of type integer-N and it uses a dual modulus prescaler. The data sheet also provides the settings for the prescaler. Hence, use the **Integer-N PLL with Dual Modulus Prescaler** from Mixed-Signal Blockset.

```

bdclose(model);

model = 'PLL_model';

open_system(model);

```

Copyright 2019 The MathWorks, Inc.

Open the mask of the PLL block and provide the specs for each of the subsystems:

- **Phase Frequency Detector** For the phase frequency detector (PFD), the data sheet does not provide any detail. Leave the deadband compensation to its default value.

- **Charge Pump** For the charge pump, the data sheet provides the typical value for the current of 2.7 mA (data sheet, Table 5). Specify the same value in the PLL model.

- VCO For the VCO, use the same specifications used in the Build VCO Model section. The

sensitivity is equal to 20 MHz/V. Specify a free running frequency that is close to the final locking

frequency, for example 4.18 GHz. Include phase noise with the same noise profile that you just

simulated.

- **Divider** For the PLL to lock at 4.2 GHz when using a reference oscillator operating at 1.6 MHz (data sheet, Figure 17), the divider ratio is equal to:

$$\frac{4.2e9}{1.6e6} = 2625$$

To achieve the effective divider ratio of 2625, set the **Prescaler divider value** to 16, **Swallow counter value** to 17, and **Program counter value** to 163.

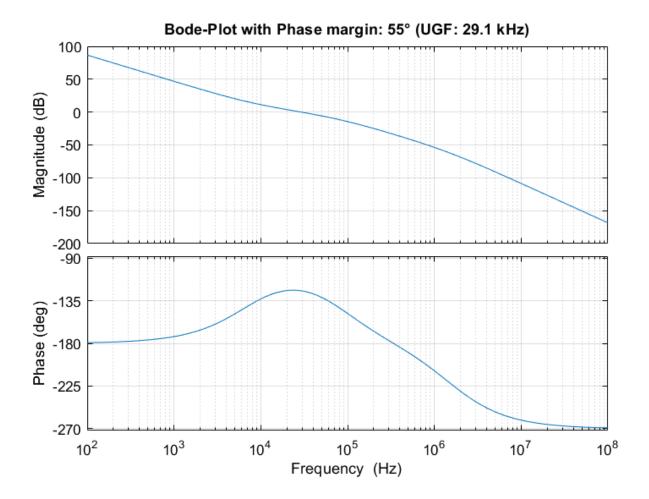

• **Loop Filter** — The data sheet provides the recommended loop filter component values in Figure 22. Manually input these values to implement the filter. Set Loop filter type to 3rd order passive. Also set the loop filter component values:

$$C1 = 100e-12 F$$

$C2 = 2.2e-9 F$

$$C3 = 100e - 12 F$$

$$R2 = 10e3 \Omega$$

$$R3 = 2.2e3 \Omega$$

Verify the closed and open loop performance of the PLL with this implementation of the loop filter. The resulting phase margin is 55 degrees. The phase margin along with the pole zero locations confirm the stability of the PLL.

Use this setup to design different loop filters and verify your design. For example, use this PLL over a different operating frequency.

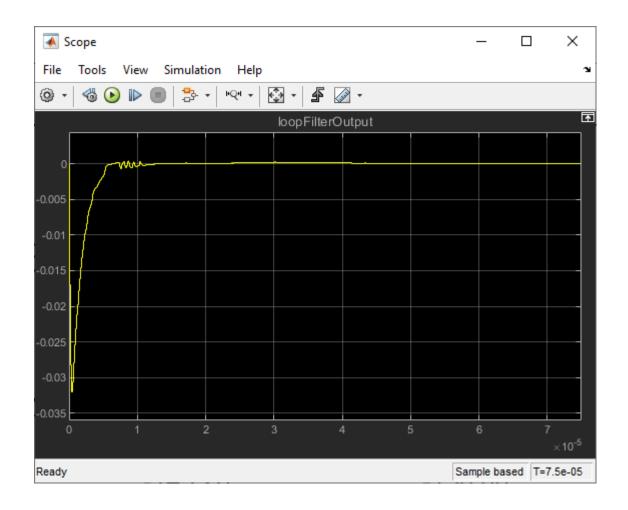

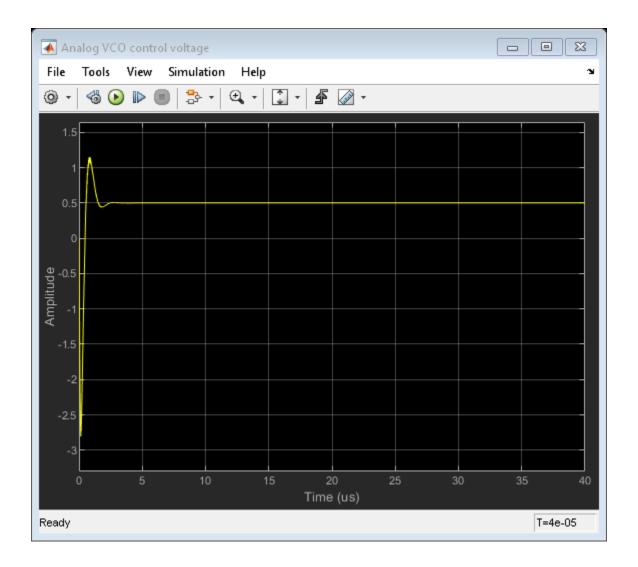

Finally, to verify the PLL locking behavior in the time domain, probe and plot the output signal of the loop filter.

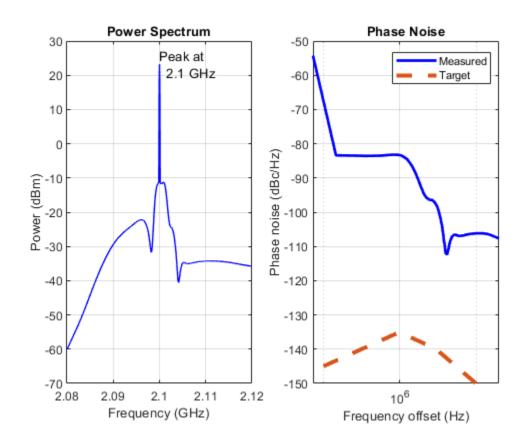

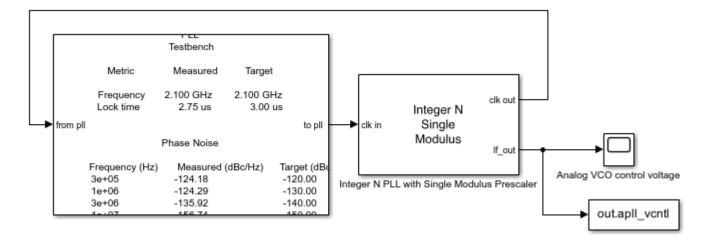

#### **Measure PLL Performance**

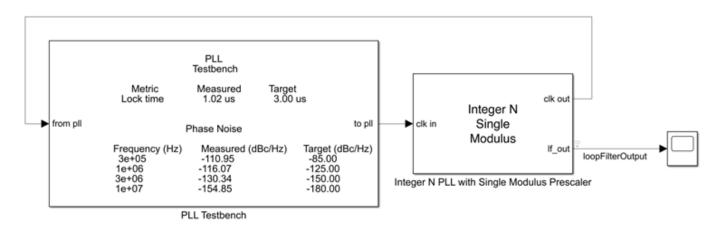

Connect the PLL to a Mixed-Signal Blockset PLL Testbench to validate its performance. The testbench defines the stimuli used to test the PLL. In this case, use a square waveform with 1.6 MHz frequency.

Set up the testbench to measure operating frequency, lock time, and phase noise. The data sheet specifies a 1 ms lock time with 1 ppm frequency error, that is to say 4.2 kHz (Table 5). Provide the same error tolerance. For measuring the phase noise, use a configuration similar to the one used for the VCO, but reduce the resolution bandwidth for higher accuracy.

For the target metric, refer to the data sheet for both the lock time (Table 5) and the closed loop phase noise measurements performed on the evaluation board (Figure 17). The phase noise profile measured at 4.2 GHz is:

- -98 dBc/Hz at 100 kHz

- -129 dBc/Hz at 1 MHz

- -150 dBc/Hz at 10 MHz

With this setup, run the PLL simulation and verify the performance.

Copyright 2019 The MathWorks, Inc

In this case, the simulation takes a few minutes. To speed up simulation time, you can relax the settings for measuring the phase noise. For example, use a larger resolution bandwidth or reduce the number of spectral averages.

The simulation results are in excellent agreement with the phase noise measurements reported in the data sheet.

#### Reference

Skyworks SKY73134-11

Copyright(C) 2019 The MathWorks, Inc. All rights reserved.

#### **See Also**

VCO | VCO Testbench | Integer N PLL with Dual Modulus Prescaler | PLL Testbench

#### **More About**

- "Design and Evaluate Simple PLL Model"

- "Phase Noise at PLL Output" on page 1-2

# **Tune Phase-Locked Loop Using Loop-Shaping Design**

This example shows how to tune the components of a passive loop filter to improve the loop bandwidth of a phase-locked loop (PLL) system. To obtain a desired loop frequency response, this example computes the loop filter parameters using the fixed-structure tuning methods provided in the Control System Toolbox<sup>TM</sup> software. The PLL system is modeled using a reference architecture block from the Mixed-Signal Blockset<sup>TM</sup> library.

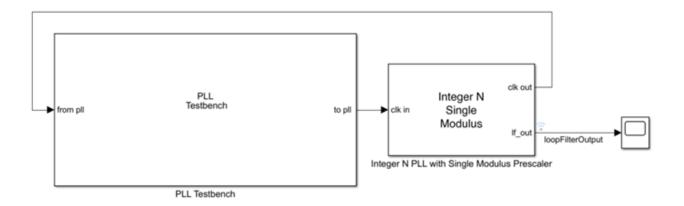

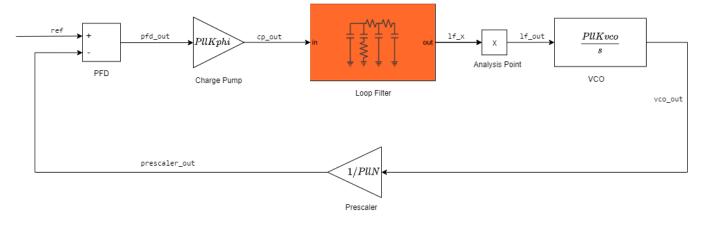

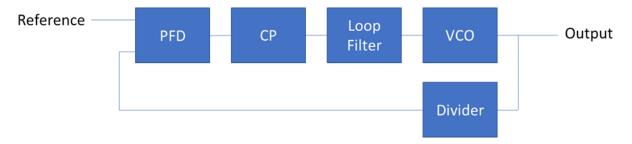

#### Introduction

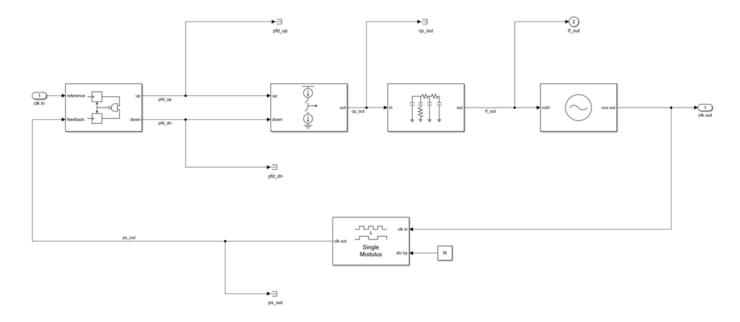

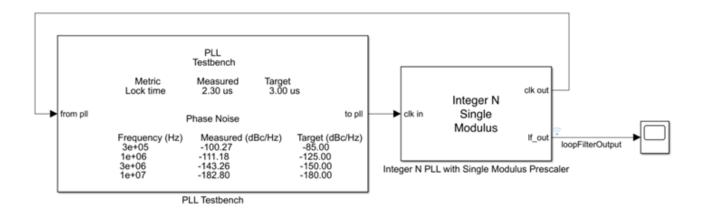

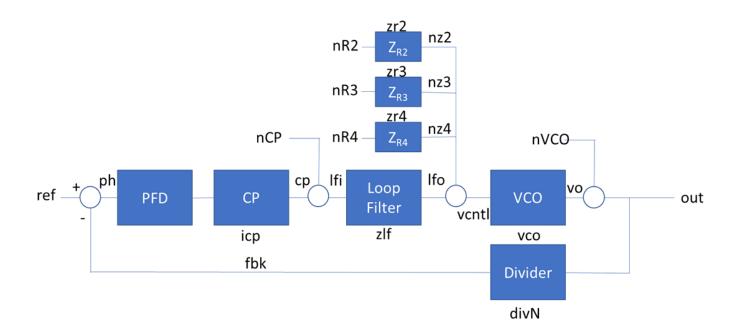

A PLL is a closed-loop system that produces an output signal whose phase depends on the phase of its input signal. The following diagram shows a simple model with a PLL reference architecture block (Integer N PLL with Single Modulus Prescaler) and a PLL Testbench block.

The closed-loop architecture inside the PLL block consists of a phase-frequency detector (PFD), charge pump, loop filter, voltage controlled oscillator (VCO), and prescaler.

The Mixed-Signal Blockset library provides multiple reference architecture blocks to design and simulate PLL systems in Simulink®. You can tune the components of the Loop Filter block, which is a passive filter, to get the desired open-loop bandwidth and phase margin.

Using the Control System Toolbox software, you can specify the shape of the desired loop response and tune the parameters of a fixed-structure controller to approximate that loop shape. For more information on specifying a desired loop shape, see "Loop Shape and Stability Margin Specifications" (Control System Toolbox). In the preceding PLL architecture model, the loop filter is defined as a fixed-order, fixed-structure controller. To achieve the target loop shape, the values of the resistances and capacitances of the loop filter are tuned. Doing so improves the open-loop bandwidth of the system and, as a result, reduces the measured lock time.

#### Set Up Phase-Locked Loop Model

Open the model.

```

model = 'PLL_TuneLoopFilter';

open_system(model)

```

The PLL block uses the configuration specified in "Design and Evaluate Simple PLL Model" for the **PFD**, **Charge pump**, **VCO**, and **Prescalar** tabs in the block parameters. The **Loop Filter** tab specifies the type as a fourth-order filter, and sets the loop bandwidth to 100 kHz and phase margin to 60 degrees. The values for the resistances and capacitances are automatically computed.

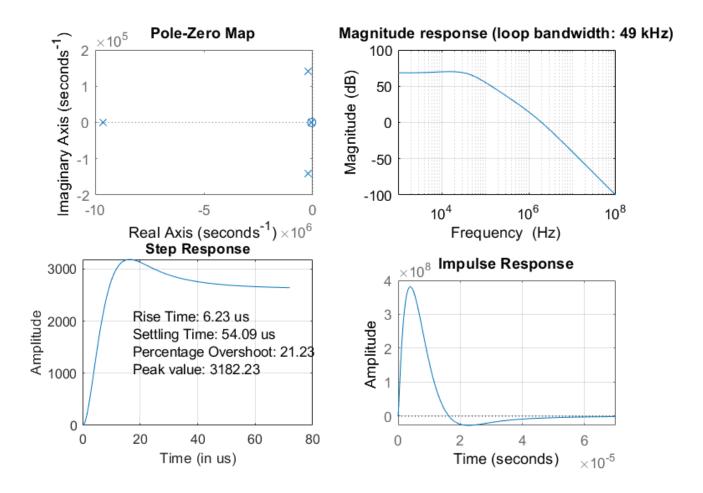

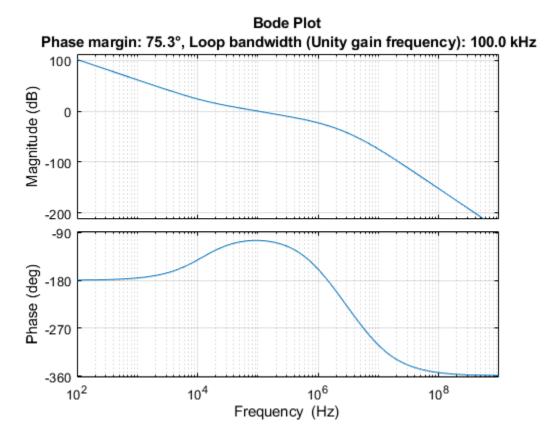

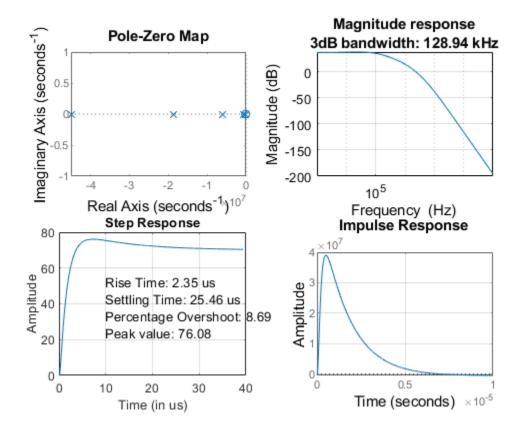

To observe the current loop dynamics of the PLL, in the block parameters, on the **Analysis** tab, select **Open Loop Analysis** and **Closed Loop Analysis**. The unity gain frequency is 100 kHz. The closed-loop system is stable and the 3-dB bandwidth is 128.94 kHz.

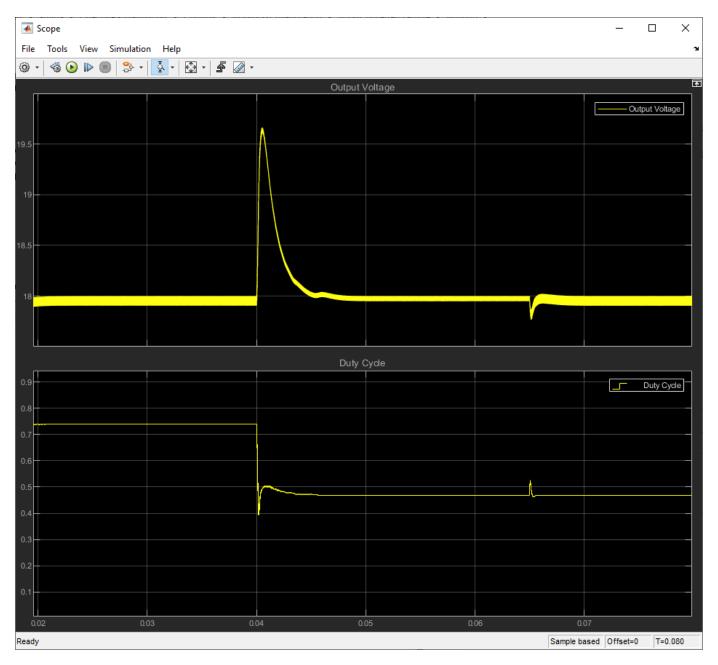

Simulate the model. The PLL Testbench block displays the PLL lock time and phase noise metrics. To plot and analyze the phase noise profile, in the PLL Testbench block parameters, on the **Stimulus** tab, select **Plot phase noise**. The measured lock time is 2.30 microseconds.

open\_system([model,'/Scope'])

sim(model);

Define the PLL parameters needed to build the closed-loop system in MATLAB®.

```

PllKphi = 5e-3;

% Charge pump output current

PllKvco = 1e8;

% VCO sensitivity

PllN

% Prescaler ratio

= 70;

PllR2

= 88.3;

% Loop filter resistance for second-order response (ohms)

PllR3

% Loop filter resistance for third-order response (ohms)

= 253:

PllR4

% Loop filter resistance for fourth-order response (ohms)

= 642;

PllC1

= 8.13e-10; % Loop filter direct capacitance (F)

= 1.48e-7; % Loop filter capacitance for second-order response (F)

PllC2

P11C3

= 1.59e-10; % Loop filter capacitance for third-order response (F)

= 9.21e-11; % Loop filter capacitance for fourth-order response (F)

PllC4

```

#### **Build Custom Tunable System**

To model the loop filter as a tunable element, first create tunable scalar real parameters (see realp (Control System Toolbox)) to represent each filter component. For each parameter, define the initial value and bounds. Also, specify whether the parameter is free to be tuned.

Use the current loop filter resistance and capacitance values as the initial numeric value of the tunable parameters.

```

% Resistances

R2 = realp('R2',PllR2);

R2.Minimum = 50;

R2.Maximum = 2000;

```

```

R2.Free = true;

R3 = realp('R3', PllR3);

R3.Minimum = 50;

R3.Maximum = 2000;

R3.Free = true;

R4 = realp('R4', PllR4);

R4.Minimum = 50;

R4.Maximum = 2000:

R4.Free = true:

% Capacitances

C1 = realp('C1',PllC1);

C1.Minimum = 1e-12;

C1.Maximum = 1e-7;

C1.Free = true;

C2 = realp('C2',PllC2);

C2.Minimum = 1e-12;

C2.Maximum = 1e-7;

C2.Free = true;

C3 = realp('C3',PllC3);

C3.Minimum = 1e-12;

C3.Maximum = 1e-7;

C3.Free = true;

C4 = realp('C4',PllC4);

C4.Minimum = 1e-12;

C4.Maximum = 1e-7;

C4.Free = true;

```

Using these tunable parameters, create a custom tunable model based on the loop filter transfer function equation specified in the More About section of the Loop Filter block reference page. loopFilterSys is a genss (Control System Toolbox) model parameterized by R2, R3, R4, C1, C2, C3, and C4.

$$Z(s) = \frac{R_2C_2s+1}{s(A_4s^3+A_3s^2+A_2s+A_1)}$$

$$A_4 = C_1C_2C_3C_4R_2R_3R_4$$

$$A_3 = C_1C_2R_2R_3(C_3+C_4) + C_4R_4(C_2C_3R_3+C_1C_3R_3+C_1C_2R_2+C_2C_3R_2)$$

$$A_2 = C_2R_2(C_1+C_3+C_4) + R_3(C_1+C_2)(C_3+C_4) + C_4R_4(C_1+C_2+C_3)$$

$$A_1 = C_1+C_2+C_3+C_4$$

$$A_1 = C_1*C_2*C_3*C_4*R_2*R_3*R_4;$$

$$A_2 = C_2*C_3*C_4*R_2*R_3*R_4;$$

$$A_3 = C_1*C_2*R_2*R_3*(C_3+C_4) + C_4*R_4*(C_2*C_3*R_3+C_1*C_2*R_2+C_2*C_3*R_2);$$

$$A_1 = C_1*C_2*R_2*R_3*(C_3+C_4) + C_4*R_4*(C_2*C_3*R_3+C_1*C_2*R_2+C_2*C_3*R_2);$$

$$A_2 = C_2*R_2*(C_1+C_3+C_4) + R_3*(C_1+C_2)*(C_3+C_4) + C_4*R_4*(C_1+C_2+C_3);$$

$$A_1 = C_1+C_2+C_3+C_4;$$

$$loopFilterSys = tf([R_2*C_2, 1], [A_4, A_3, A_2, A_1, 0]);$$

Use the transfer function representations to define the fixed blocks in the architecture (charge pump, VCO, and prescaler), based on their respective frequency response characteristics [1].

Define input and output names for each block. Connect the elements based on signal names (see connect (Control System Toolbox)) to create a tunable closed-loop system (see genss) representing the PLL architecture as shown.

```

chargePumpSys.InputName = 'pfd out';

% Charge pump (fixed block)

chargePumpSys.OutputName = 'cp out';

loopFilterSys.InputName = 'cp out';

% Loop filter (tunable block)

loopFilterSys.OutputName = 'lf x';

AP = AnalysisPoint('X');

% Analysis point does not change the archite

AP.InputName = 'lf_x';

AP.OutputName = 'lf out';

vcoSys.InputName = 'lf out';

% VCO (fixed block)

vcoSys.OutputName = 'vco out';

prescalerSys.InputName = 'vco out';

% Prescaler (fixed block)

prescalerSys.OutputName = 'prescaler_out';

pfd = sumblk('pfd_out = ref - prescaler_out');

% Phase-frequency detector (sum block)

% Create a genss model for the closed-loop architecture

CL0 = connect(chargePumpSys,loopFilterSys,AP,vcoSys,prescalerSys,pfd,'ref','vco_out');

```

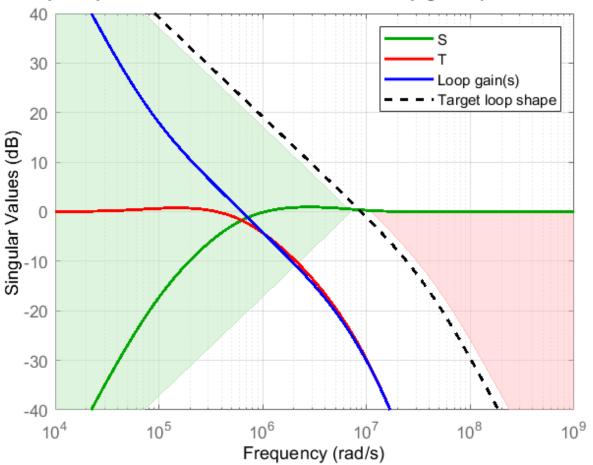

#### Loop-Shaping Design

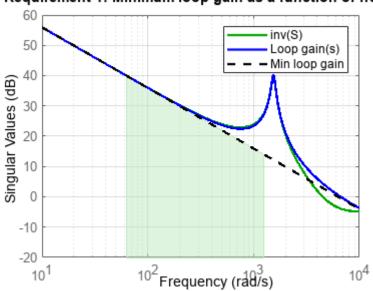

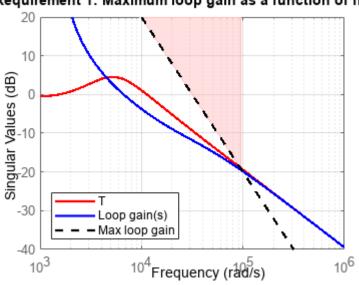

Define the loop gain as a frequency-response data model by providing target gains for at least two decades below and two decades above the desired open-loop bandwidth. The desired roll-off is typically higher, which results in a higher attenuation of phase noise.

Specifying the appropriate target loop shape is the critical aspect of this design. The tunable compensator is a fourth-order system with a single integrator and a single zero, and the plant represents an integrator. The loop gains must be a feasible target for the open-loop structure.

For tuning the loop filter, create a tuning goal based on a target loop shape specifying the integral action, a 3 MHz crossover, and a roll-off requirement of 40 dB/decade. The goal is enforced for three decades below and above the desired open-loop bandwidth.

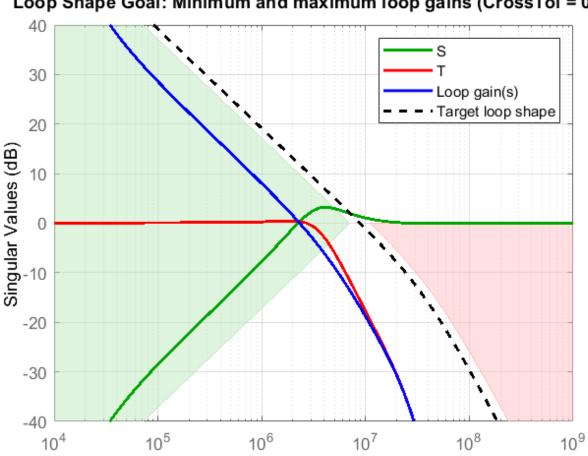

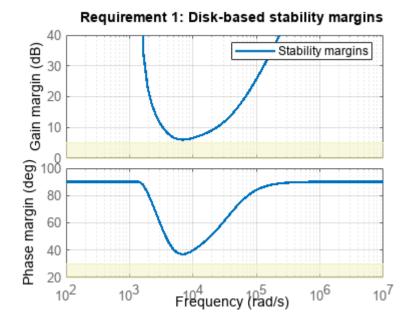

Observe the current open-loop shape of the PLL system with reference to the target loop shape. **S** represents the inverse sensitivity function and **T** represents the complementary sensitivity function. By default, Control System Toolbox plots use rad/s as the frequency unit. For more information on how to change the frequency unit to Hz, see "Toolbox Preferences Editor" (Control System Toolbox).

figure

viewGoal(LoopShapeGoal,CL0)

MarginsGoal.Name = 'Margins Goal';

## Loop Shape Goal: Minimum and maximum loop gains (CrossTol = 0.1)

Use systune to tune the fixed-structure feedback loop. Doing so computes the resistance and capacitance values to meet the soft design goal based on the target loop shape. Run the tuning algorithm with five different initial value sets in addition to the initial values defined during the creation of the tunable scalar real parameters.

```

Options = systumeOptions();

Options.SoftTol = 1e-5;

% Relative tolerance for termination

Options.MinDecay = 1e-12;

% Minimum decay rate for closed-loop poles

Options.MaxRadius = 1e12;

% Maximum spectral radius for stabilized dynamics

Options.RandomStart = 5;

% Number of different random starting points

[CL,fSoft,gHard,Info] = systune(CL0,[LoopShapeGoal; MarginsGoal],[],Options);

Final: Soft = 3.16, Hard = -Inf, Iterations = 79

Final: Failed to enforce closed-loop stability (max Re(s) = 3.1e+04)

Final: Failed to enforce closed-loop stability (max Re(s) = 6.7e+04)

Final: Failed to enforce closed-loop stability (max Re(s) = 6.3e+04)

Final: Failed to enforce closed-loop stability (max Re(s) = 7.5e+04)

Final: Failed to enforce closed-loop stability (max Re(s) = 4.9e+04)

```

systune returns the tuned closed-loop system CL in generalized state-space form.

The algorithm fails to converge for the random initial values, and provides a feasible solution only when the current loop filter component values are chosen as the initial conditions. For tuning problems that are less complex, such as a third-order loop filter, the algorithm is less sensitive to initial conditions and randomized starts are an effective technique for exploring the parameter space and converging to a feasible solution.

Examine the tuned open-loop shape with reference to the target loop shape. Observe that while the tuned loop shape does not meet the target, the open-loop bandwidth increases while the loop keeps the same high-frequency attenuation.

```

figure

viewGoal(LoopShapeGoal,CL)

```

## Loop Shape Goal: Minimum and maximum loop gains (CrossTol = 0.1)

#### **Export Results to Simulink Model**

Extract the tuned loop filter component values.

```

Rtuned = [getBlockValue(CL, 'R2'),...

getBlockValue(CL, 'R3'),...

getBlockValue(CL, 'R4')];

Ctuned = [getBlockValue(CL, 'C1'),...

getBlockValue(CL, 'C2'),...

getBlockValue(CL, 'C3'),...

getBlockValue(CL, 'C4')];

```

Write the tuned loop filter component values to the PLL block using the setLoopFilterValue helper function provided with the example.

Frequency (rad/s)

```

blk = [model,'/Integer N PLL with Single Modulus Prescaler'];

setLoopFilterValue(blk,Rtuned,Ctuned);

```

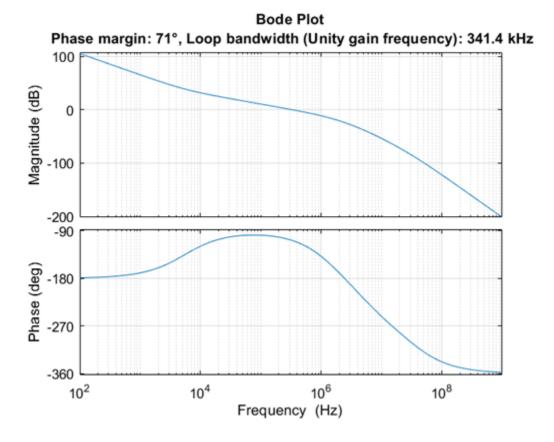

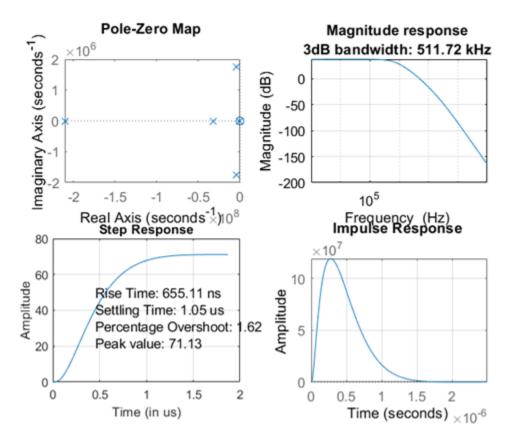

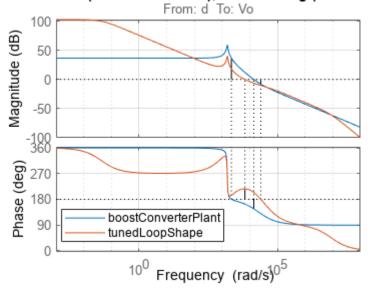

Observe the Open Loop Analysis and Closed Loop Analysis plots from the **Analysis** tab in the Integer N PLL with Single Modulus Prescaler block parameters. The unity gain frequency and the 3-dB

bandwidth show improvement and are now  $341.4~\mathrm{kHz}$  and  $511.72~\mathrm{kHz}$ , respectively, while the loop keeps the same phase noise profile.

Simulate the model and get the PLL Testbench measurements and loop filter output with the tuned components.

sim(model);

## **References**

[1] Banerjee, Dean. *PLL Performance, Simulation and Design*. Indianapolis, IN: Dog Ear Publishing, 2006.

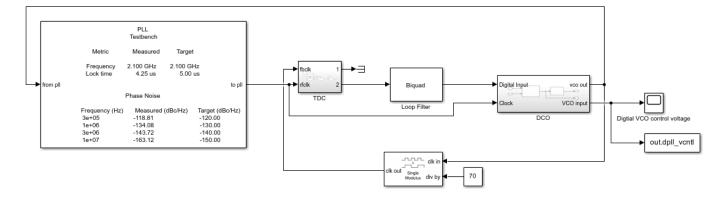

# **Digital Phase Locked Loop**

This example shows how to model a digital phase locked loop using the Mixed-Signal Blockset<sup>TM</sup>. In a digital phase locked loop, phase detection is performed by a time to digital converter (TDC), loop filtering is performed by a digital filter, and the oscillator is a digitally controlled oscillator (DCO). This example demonstrates a behavioral model of a TDC, using the BiquadFilter from the DSP System Toolbox<sup>TM</sup> as the digital loop filter, and using VCOs and DACs from the Mixed-Signal Blockset to model the DCO.

This example also demonstrates one method for designing the control loop of a digital PLL by using the PLL architectures from the Mixed-Signal Blockset to design an analog PLL and then translate the analog design to its digital equivalent.

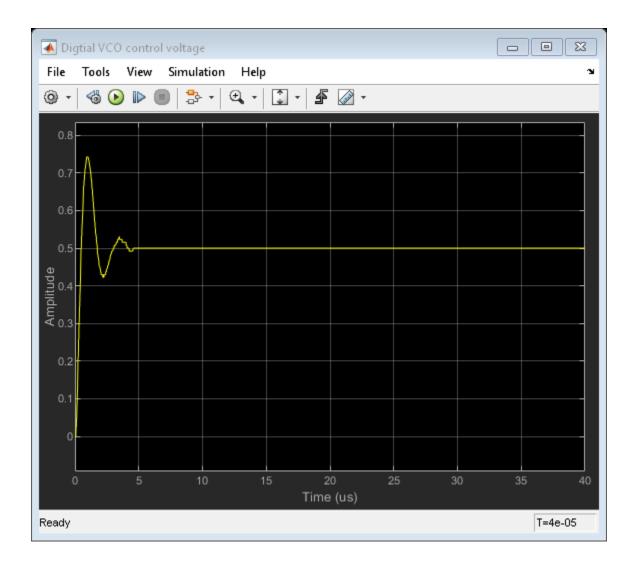

#### **Digital PLL**

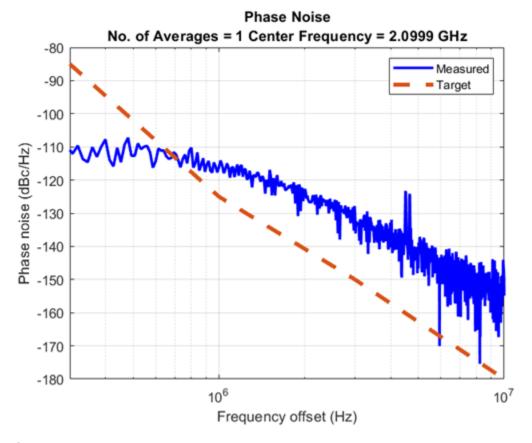

Open and run the example model of a digital PLL. Then select the PLL Testbench in the model and click the Plot phase noise button (or call the button's callback function). Save loop filter waveform and phase noise data for later comparison to analog PLL results.

```

open('DigitalPLL.slx');

simout = sim(bdroot);

msblks.PLL.pllTBPlotPhaseNoiseButton([bdroot '/PLL Testbench']);

dpll_vcntl = simout.dpll_vcntl;

getDigitalPllPhaseNoise;

```

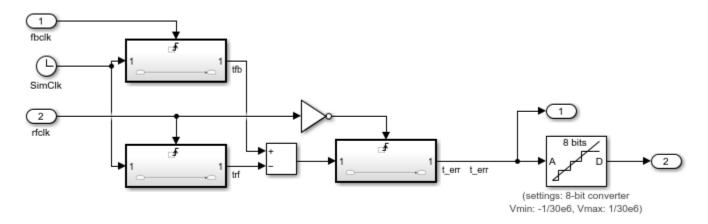

## **Time to Digital Converter**

The behavioral model of the TDC uses triggered subsystems to sample the clock time at the rising edges of the reference clock and the PLL's fractional divider. It then calculates the difference between these two sampled clock times and converts to an eight bit integer output value. To model a digital feedback loop clocked by the reference, the output port sample rate is set to the reference frequency.

open system('DigitalPLL/TDC', 'force');

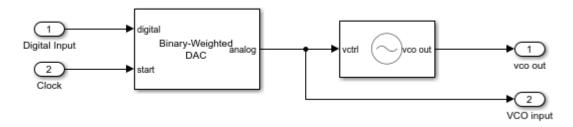

## **Digital Controlled Oscillator**

The DCO model represents a circuit in which the control for a VCO is set by a digital to analog converter (DAC). The conversion in the DAC is triggered by the reference clock.

The phase noise impairment in the VCO is enabled. The DAC model can also model impairments. However the DAC impairments are not enabled in the example model.

You could alternatively model a DCO by directly setting a Mixed-Signal Blockset VCO's control voltage array to an array of consecutive integers that spans the range of digital input values. Then you can set the output frequency array to supply the output frequency for each possible input value.

open\_system('DigitalPLL/DCO','force');

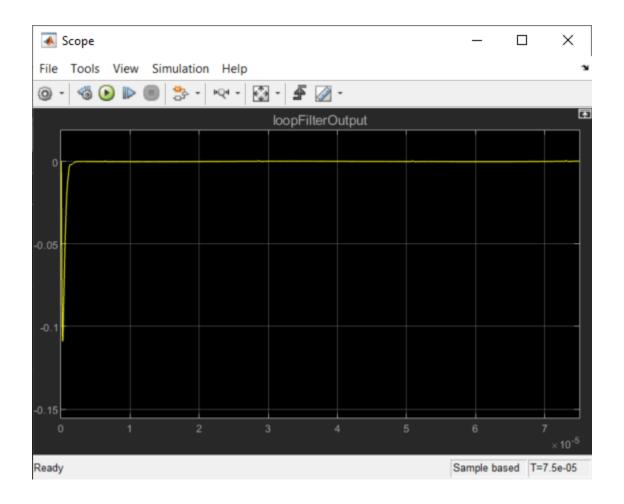

## **Digital Loop Filter**

The loop filter is a BiquadFilter from the DSP System Toolbox. It is clocked at the reference clock frequency by the output port of the TDC.

The digital loop filter is designed using the automated design feature of the Integer N PLL with Single Modulus Prescaler model from the Mixed-Signal Blockset PLL Architectures library. An analog loop filter is designed to achieve a specified loop bandwidth and phase margin, then the circuit values and sample interval are translated to digital filter coefficients. To obtain the correct overall loop gain, a scale factor is applied to the biquad filter model of the loop filter.

The derivation of the loop gain scale factor parallels that of A Design Procedure for All-Digital Phase-Locked Loops Based on a Charge-Pump Phase-Locked-Loop Analogy.

The variables used in the derivation are

- Icp Charge pump maximum current amplitude

- Z(s) Analog loop filter transfer impedance

- Kvco VCO sensitivity for both analog and digital PLLs

- Tref Reference clock period

- $\Delta_{TDC}$  TDC time resolution

- H(s) Digital loop filter transfer function

- $K_{DAC}$  DAC gain

Note that for this example, the total range of the TDC is two reference clock periods.

The equation to make the loop gain of the analog and digital PLLs equal is:

$$\frac{I_{CP}}{2\pi}Z\left(s\right)\frac{K_{VCO}}{s} = \frac{2T_{REF}}{2\pi}\frac{1}{\Delta_{TDC}}H\left(s\right)K_{DAC}\frac{K_{VCO}}{s}$$

Since the TDC and the DAC in this example have been configured to have the same number of bits, this equation reduces to:

$$H\left(s\right) = \frac{I_{CP}}{2}Z\left(s\right)$$

Since the function getSOSfromAnalogPLL included in this example produces filter coefficients that result in a filter gain Z(s), the scale factor for the loop filter is  $\frac{I_{CP}}{2}$ .

While the loop filter coefficients, input signal and output signal in this example are all double precision floating point, it would also be possible to use Fixed-Point Designer $^{\text{\tiny TM}}$  to model the entire digital feedback path using exactly the same digital precision as in the circuit design, thus obtaining even more precise evaluation of impairments such as quantization noise.

You can design and configure the digital loop filter by running the script:

%%designDigitalLoopFilter;

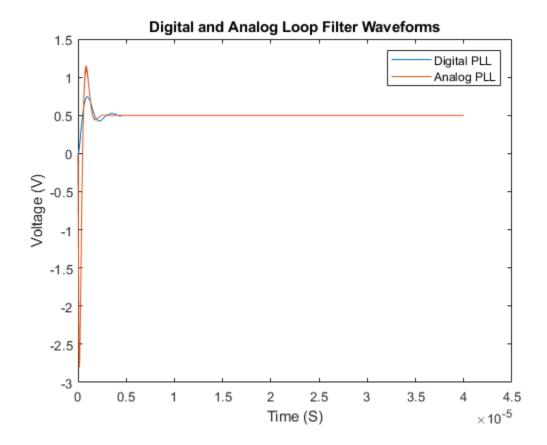

#### Compare to Analog PLL

You can compare the loop acquisition of the analog PLL to that of the digital PLL. The additional high frequency ripple in the analog loop filter response is due to the charge pump waveform.

```

open('AnalogPLL.slx');

simout = sim(bdroot);

apll_vcntl = simout.apll_vcntl;

plotLoopFilterWaveforms;

msblks.PLL.pllTBPlotPhaseNoiseButton([bdroot '/PLL Testbench']);

plot(xdpll,ydpll,'LineWidth',2,'DisplayName','Digital PLL');

```

## Model PLLs in the Phase Domain

This example shows how to model a phase-locked loop (PLL) in the phase domain, compare the analytic results to simulation results in the time domain, and identify the advantages and disadvantages of each approach. Most PLL analysis is performed in the phase domain, and this example shows you how to produce a complete analysis using a minimum of time and effort.

The phase domain analysis calculates the PLL transfer function, loop error function, lock time and noise transfer impedances using the Control System Toolbox $^{\text{m}}$ . (Automated loop tuning is described in the "Tune Phase-Locked Loop Using Loop-Shaping Design" on page 1-23 example.)

The PLL design and the time domain simulation model were derived from the "Phase Noise at PLL Output" on page 1-2 example.

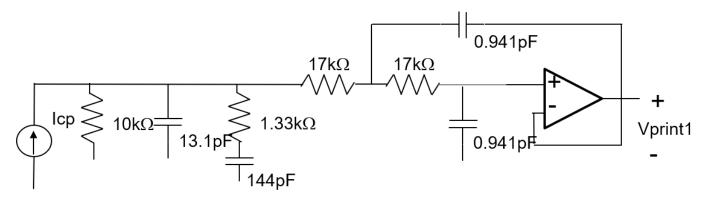

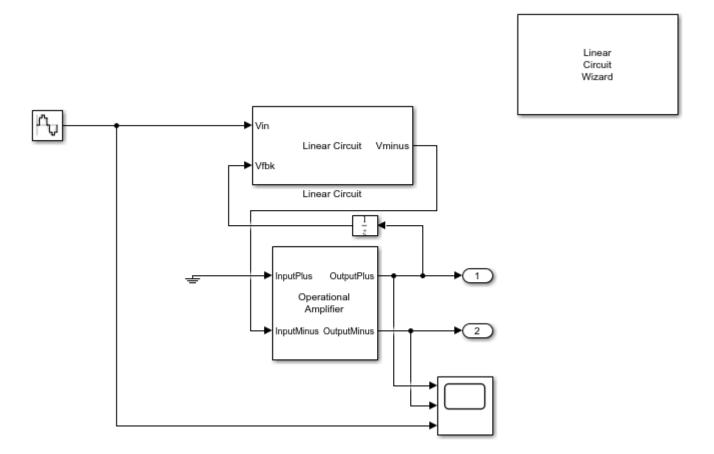

The general loop filter modeling procedure uses the Mixed-Signal Blockset<sup>™</sup> Linear Circuit Wizard and was derived from the "Circuit Design Details Affect PLL Performance" on page 3-16 example.

#### **Phase Domain Block Models**

This section shows how to create the phase domain models for the individual blocks of an analog phase/frequency locked loop.

The term phase domain refers to the representation of a periodic signal in terms of its phase with respect to an ideal reference with the same period, instead of in terms of its voltage or current as a function of time. Most PLL analyses (in contrast with simulations) treat the PLL as a linear control system in the frequency domain, with the reference signal and the output of the VCO/divider represented in the phase domain.

The Control System Toolbox supports both transfer function (tf) and state space (ss) models. While the tf objects tend to be easier to use, the ss objects are often more accurate at higher frequencies.

To enable comparison of analysis results to time domain simulation results, this example uses the same design values as the Phase noise at PLL output example.

```

% Charge Pump output current

PllKphi = 5e-3;

PllKvco = 100e6;

% VCO sensitivity

PllN

= 70;

% Prescaler ratio

PllR2

= 1.33e3;

% Loop filter resistance for second order response (ohms)

PllR3

= 1.7e4;

% Loop filter resistance for third order response (ohms)

PllR4

= 0;

% Loop filter resistance for fourth order response (ohms)

PllC1

= 1.31e-11; % Loop filter direct capacitance (F)

PllC2

= 1.44e-10; % Loop filter capacitance for second order response (F)

PllC3

= 9.41e-13; % Loop filter capacitance for third order response (F)

% Loop filter capacitance for fourth order response (F)

PllC4

```

#### Reference

The reference signal is assumed to have the same frequency as the ideal reference used to define the phase domain. However, there can be a time-varying phase offset between the reference signal and the ideal reference. This phase offset  $\theta_{ref}(t)$ , or  $\theta_{ref}(s)$  in the Laplace domain, is an input to the linear control system.

#### VCO and Clock Divider

The VCO output phase is the integral of the VCO control voltage.

$$\theta_{VCO}(t) = \int 2\pi K_{VCO} V_{CNTL}(t) dt$$

Or, in the Laplace domain,

$$\theta_{VCO}(s) = \frac{2\pi K_{VCO}}{s} V_{CNTL}(s)$$

From this equation, the statement to construct an ss model of the VCO is

$$vco = ss(0,2*pi*PllKvco,1,0);$$

Given a divider ratio PllN (not necessarily integer), the ss object for the divider is

$$divN = ss(0,0,0,1/PllN);$$

The VCO also has phase noise at its output, characterized as a phase noise density  $n_{VCO}(f)$ , filtered by the closed loop gain of the PLL.

## Phase/Frequency Detector (PFD) and Charge Pump (CP)

Given phase domain inputs  $\theta_{ref}(t)$  and  $\theta_{VCO}(t)$ , and maximum output current  $I_{CP}$ , the average output current of the PFD/CP is:

$$i_{CP}(t) = (\theta_{ref}(t) - \theta_{VCO}(t)) \frac{I_{CP}}{2\pi}$$

Or in the Laplace domain:

$$i_{CP}(s) = (\theta_{ref}(s) - \theta_{VCO}(s)) \frac{I_{CP}}{2\pi}$$

The CP also has phase noise at its output, characterized as a phase noise density  $n_{CP}(f)$ .

#### **Loop Filter**

The loop filter presents a transfer impedance  $Z_{LF}(s)$  to the CP output, thus converting the CP output current to a control voltage applied to the VCO. [1] describes a family of widely used second, third and fourth order loop filters. More convenient modeling of this and other loop filter circuit designs using the Linear Circuit Wizard is described in the General Loop Filters section below.

The second order filter is described by the equation

$$Z_2(s) = \frac{1 + sR_2C_2}{s(C_1 + C_2)(1 + sR_2\frac{C_1C_2}{C_1 + C_2})}$$

The higher order filters are formed by adding a series R/shunt C section. Given an k-1 order filter design for which  $Z_{(k-1)}(s) = (b(s))/(a_{(k-1)}(s))$ , followed by series resistor  $R_k$  and shunt capacitor C k, the transfer impedance of the higher order filter is

$$Z_k(s) = \frac{b(s)}{a_{k-1}(s)(1 + sR_kC_k) + sC_kb(s)}$$

One way to transform these equations into an ss object is to calculate the transfer function coefficients and then use the tf2ss function. Given that the filter has nsections sections, with corresponding element values, the procedure is

The resistors in the loop filter also produce Johnson noise. This noise can be modeled as a noise current that is then applied to a transfer impedance to produce a noise voltage at the output of the loop filter. Given a resistance R, the current spectral density is  $\frac{4kT}{R}$  Watts/Hz, where k is Boltzmann's constant and T is the absolute temperature.

The noise transfer impedance calculation follows a very similar process as that for the overall loop filter transfer impedance. However it must be calculated separately for each resistor in the loop filter. The function getNoiseTransferImpedance(R,C,n) included with this example produces an ss model for the device noise transfer impedance of the resistor  $R_n$ .

#### **Control Loop Analysis**

This section shows how to perform numerous open and closed loop analyses using the phase domain models of the PLL blocks. The process is to first create a closed loop system model and then invoke functions that perform the desired analysis using that model.

Most of the analyses only require a single input, single output model of the PLL, and so you will define that model first. The noise filtering analysis requires a multiple input model, and you will define that in the noise filtering section.

In PLL control loop modeling the divider ratio N is usually kept separate from the gain G due to the PFD/CP, loop filter, and VCO.

$$G(s) = \frac{I_{CP}}{2\pi}Z(s)\frac{2\pi K_{VCO}}{s} = \frac{I_{CP}Z(s)K_{VCO}}{s}$$

The loop transfer function (from reference input to VCO output) is

$$H(s) = \frac{G(s)}{(1 + G(s)/N)}$$

The corresponding MATLAB code is

```

G = PllKphi/2/pi*zlf*vco;

H = feedback(G,divN);

H.InputName = 'ref';

H.OutputName = 'out';

```

## **Closed Loop Transfer Function**

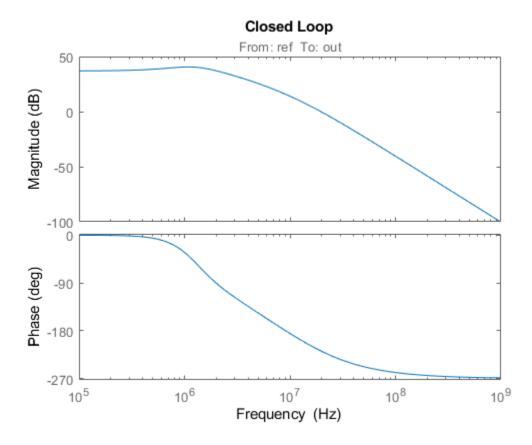

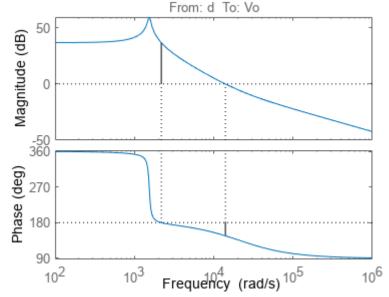

Use the bode function to plot the magnitude and phase of the closed loop transfer function.

NOTE: Configure the bode function to scale the frequency in Hz and not rad/s.

```

figure(1);

opts = bodeoptions('cstprefs');

opts.FreqUnits = 'Hz';

bodeplot(H,opts);

title('Closed Loop');

```

You can also use other variants of the bode function to output results to the workspace for use in other analyses.

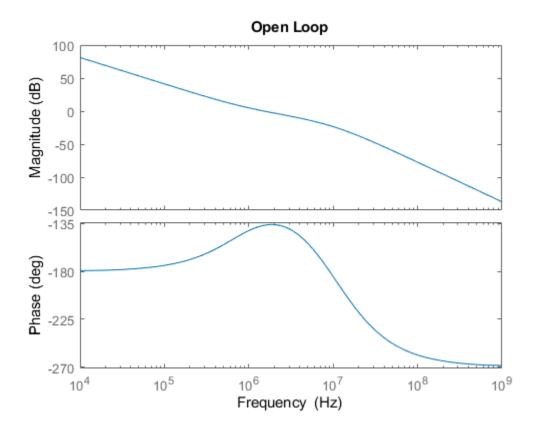

## **Loop Stability**

Use the bode function again to plot the magnitude and phase of the loop gain, only this time use the series function instead of the feedback function

```

GoverN = series(G,divN);

figure(2);

bodeplot(GoverN,opts);

title('Open Loop');

```

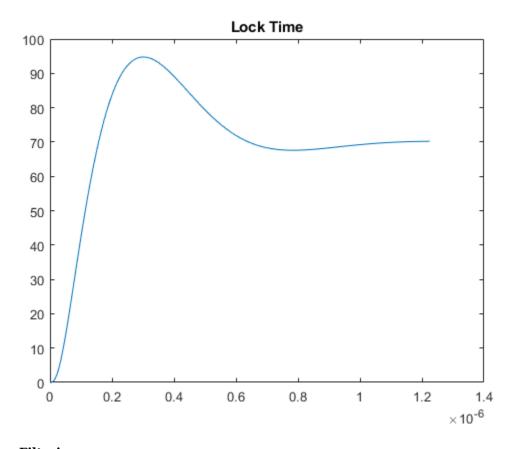

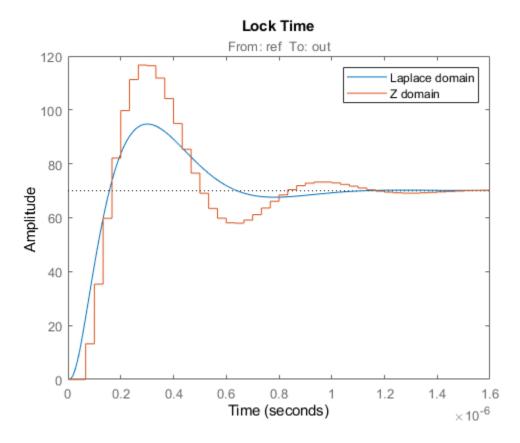

## **Lock Time**

Obtain the loop lock time from the loop step response.

```

figure(3);

[ystep,tstep] = step(H);

plot(tstep,ystep);

title('Lock Time');

```

## **Noise Filtering**

The analysis of noise filtering usually requires multiple inputs- one for each noise source. While such a model could be used for all the analyses presented earlier in this section, that would complicate the coding without providing additional insight. The required block diagram is shown below.

The procedure is to use the connect function to obtain a transfer function from each noise source to the PLL output, apply each of these transfer functions to their respective noise source, and then plot the resulting output noise spectral densities.

The zlf, vco, and divN blocks are already defined.

Define blocks required for noise filtering analysis.

R = [PllR2, PllR3, PllR4];

C = [PllC1, PllC2, PllC3, PllC4];

```

zr2 = getNoiseTransferImpedance(R,C,2);

zr3 = getNoiseTransferImpedance(R,C,3);

The example loop filter is third order. No need for zr4.

icp = ss(0,0,0, PllKphi/2/pi);

sum1 = sumblk('ph = ref - fbk');

sum2 = sumblk('lfi = cp + nCP');

sum3 = sumblk('vcntl = lfo + nz2 + nz3');

sum4 = sumblk('out = vo + nVCO');

zlf.InputName = 'lfi';

zlf.OutputName = 'lfo';

vco.InputName = 'vcntl';

vco.OutputName = 'vo';

divN.OutputName = 'fbk';

divN.InputName = 'out';

icp.InputName = 'ph';

icp.OutputName = 'cp';

zr2.InputName = 'nR2';

zr2.OutputName = 'nz2';

zr3.InputName = 'nR3';

zr3.OutputName = 'nz3';

Connect the PLL as a control system.

Hnoise = connect(icp,zlf,vco,divN,zr2,zr3,sum1,sum2,sum3,sum4,...

{'ref', 'nCP', 'nR2', 'nR3', 'nVCO'}, 'out');

Href = Hnoise(1,1);

Hncp = Hnoise(1,2);

```

```

Hnr2 = Hnoise(1,3);

Hnr3 = Hnoise(1,4);

Hnvco = Hnoise(1,5);

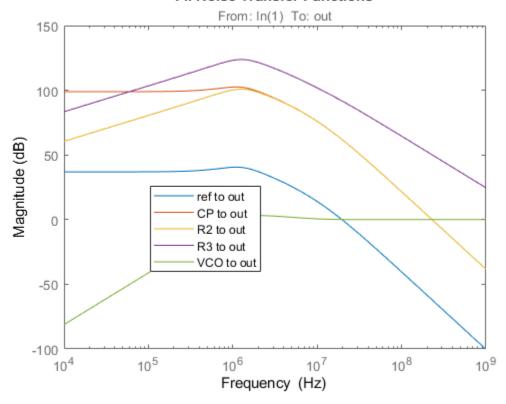

Plot the transfer functions

figure(4);

opts.PhaseVisible = 'off';

bodeplot(Href,Hncp,Hnr2,Hnr3,Hnvco,opts);

title('Pll Noise Transfer Functions');

legend('ref to out','CP to out','R2 to out','R3 to out','VCO to out');

```

#### PII Noise Transfer Functions

## **Output Noise Spectral Density**

Each of the PLL's internal noise sources can have a flicker noise component (1/f) as well as an additive white Gaussian noise (AWGN) component that is flat with frequency. In this section you will model the combination of these two components as an AWGN process driving a single filter with a gain that is unity at high frequencies but increases as 1/f below a predefined corner frequency. The getFlickerFilter function supplied with this example provides a useful approximation.

The model for the VCO phase noise n\_VCO can be obtained from the measured or specified phase noise of the VCO using the process defined for the MSB Ring Oscillator model. This process fits the measured data to a physical model of the VCO (including flicker noise) while avoiding a couple of inaccuracies present in most oscillator phase noise measurements. While the Ring Oscillator model process produces a period offset standard deviation, the application to phase domain modeling requires that the period offset be scaled to a phase offset.

You can derive the  $n_{VCO}$  model for the time domain simulation used in this example using the following steps.

```

PllFoffset = [30e3 100e3 1e6 3e6 10e6]; % VCO offset frequencies (Hz)

PllPhaseNoise = [-56 -106 -132 -143 -152]; % VCO output phase noise (dBc/Hz)

CfgRef = 30e6; % Reference frequency

f0 = PllN*CfgRef;

[periodjitter,fcorner] = ...

msblks.VCO.estimatePhaseNoiseCore(f0,PllFoffset,PllPhaseNoise);

phasejitter = 2*pi*f0*periodjitter; % Convert from period jitter to phase jitter

% Scale for the fact that the phase jitter occurs in one VCO output cycle.

n VCO = ss(0,sqrt(f0)*phasejitter,1,0) * qetFlickerFilter(fcorner);

```

You can model the Johnson current noise in the loop filter resistors by multiplying the broadband current noise density times a flicker filter. Due to the high quality of modern manufacturing, the typical corner frequency for a resistor is somewhere between 1kHz and 10kHz.

```

kB = 1.3805e-23; % Boltzmann's constant

temp = 273 + 25; % Temperature, in degrees Kelvin for an ambient of 25C

fc_resistors = 3e3; % Typical resistor flicker corner frequency

n_r2 = sqrt(4*kB*temp/PllR2)*getFlickerFilter(fc_resistors);

n_r3 = sqrt(4*kB*temp/PllR3)*getFlickerFilter(fc_resistors);

```

The CP is an active circuit, and the noise it generates is determined by details of the circuit design and device parameters. Its noise density is best obtained from device data sheets. However at least one version of such data data sheet parameters [1] characterizes the noise at the output of the PLL and not the output of the charge pump.

For the sake of having some sort of model, suppose that

- 1. In steady state operation, on average one or the other CP output transistor is operating with a duty cycle d. 0.01 < d < 0.1

- 2. When one of the CP output transistors is on, its  $V_{DS} = 0$  channel conductivity  $g_{ds}$  is  $g_{ds} = \frac{I_{CP}}{A*V_{DD}}$  where  $1 <= V_{DD} <= 5$  and the saturation factor 2 < A < 10.

- 3. The channel current integration constant is  $2/3 <= \gamma < 1.5$

Then the CP current noise spectral density is  $\sqrt{4kTd\gammarac{I_{CP}}{A*V_{DD}}}$

```

CP_d = 0.03;

CP_A = 4;

CP_VDD = 5;

CP_gamma = 1;

n_CP = sqrt(4*kB*temp*CP_d*CP_gamma*PllKphi/CP_A/CP_VDD)*...

getFlickerFilter(fc_resistors);

```

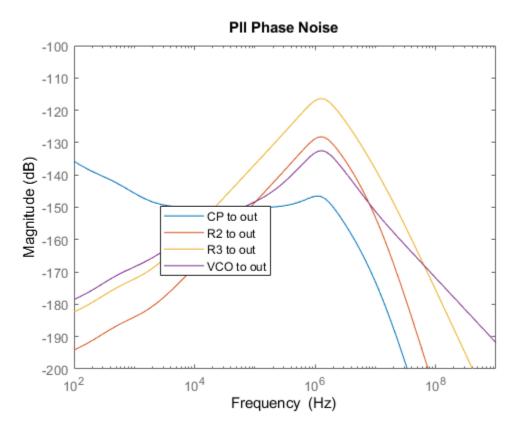

Plot the phase noise contributions for all four noise sources.

```

figure(5);

opts.PhaseVisible = 'off';

opts.MagLowerLimMode = 'manual';

opts.MagLowerLim = -200;

opts.XLimMode = 'manual';

```

```

opts.XLim = [100,1e9];

nout_CP = n_CP*Hncp;

nout_R2 = n_r2*Hnr2;

nout_R3 = n_r3*Hnr3;

nout_VCO = n_VCO*Hnvco;

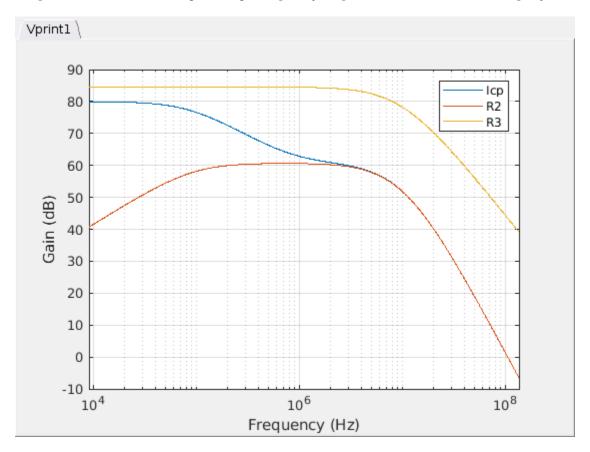

bodeplot(nout_CP,nout_R2,nout_R3,nout_VCO,opts);

title('Pll Phase Noise');

legend('CP to out','R2 to out','R3 to out','VCO to out');

opts.PhaseVisible = 'on';

opts.MagLowerLimMode = 'auto';

opts.XLimMode = 'auto';

```

#### Compare to time domain results

This section compares the phase domain analysis results to the results of a time domain simulation using the model presented in the "Phase Noise at PLL Output" on page 1-2 example. The clearest and most direct approach is to compare the step response predicted by the analysis with the phase lock response produced by the simulation.

The PllPhaseNoiseExample.slx model included with this example is statically configured for the purposes of this section. The workspace output and a CP output monitor port give you access to additional data when performing follow-on investigations such as are suggested in this section and the Compare Z domain with Laplace domain subsection.

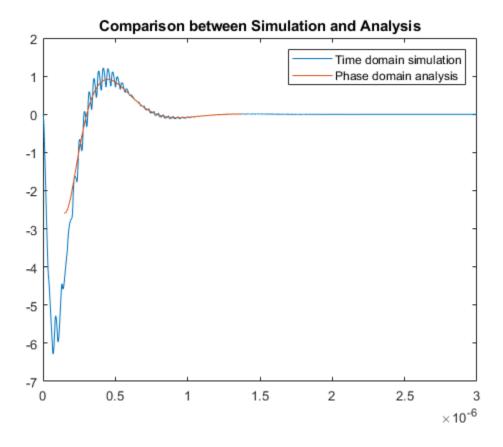

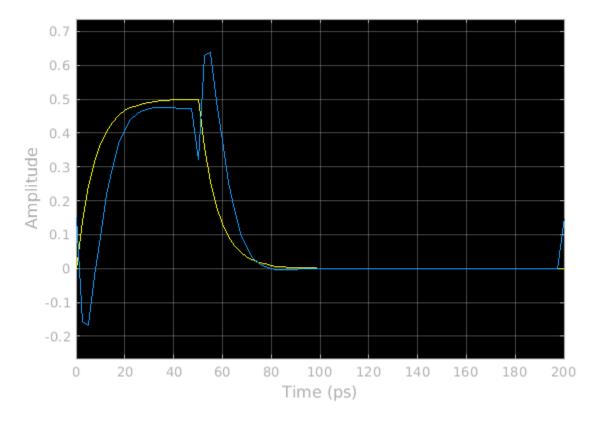

Run the time domain simulation and compare the loop lock response to a manually adjusted copy of the phase domain step response.

```

open_system('PllLoopDynamicsExample.slx');

out = sim('PllLoopDynamicsExample.slx');

figure(6);

plot(out.vco_in.Time,squeeze(out.vco_in.Data));

hold on;

plot(tstep+1.46e-7,0.913/24.7*(ystep-70));

title('Comparison between Simulation and Analysis')

legend('Time domain simulation','Phase domain analysis')

```

The time domain loop lock response agrees quite well with the phase domain analysis result. It is interesting that there is a portion of the time domain response that precedes the phase domain step response. Using features explained in the following paragraph, you can demonstrate that this phenomenon occurs even for very small phase steps, and is therefore a linear response phenomenon.

As an aid to further study, the reference phase modulator in the model has been configured to produce a PRBS6 modulation with a long enough period to capture the entire step response, and a low enough amplitude to assure operation within the linear range. You can explore the resulting behaviors by toggling the switch at the output of the reference phase modulator, and you may also find it helpful to examine the CP output to verify operation in the linear range.

Because of the very high loop bandwidth, some leakage of the high frequency portions of the CP output are clearly visible in the loop filter output. These high frequency perturbations modulate the VCO frequency and cause spurious responses at the output of the PLL. Phase domain analysis does not address these spurious responses.

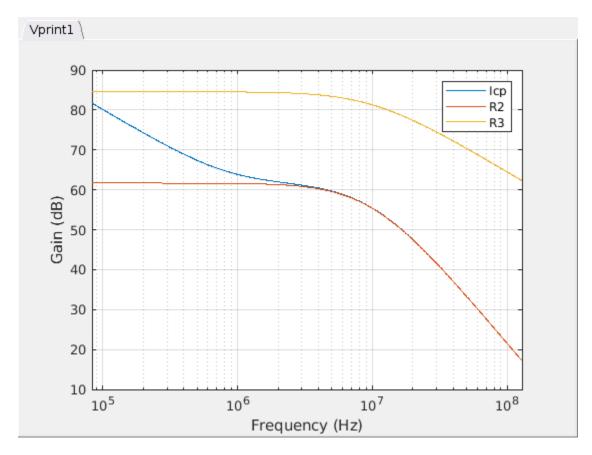

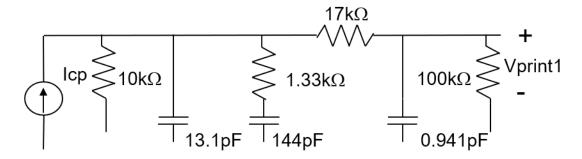

#### **General Loop Filters**

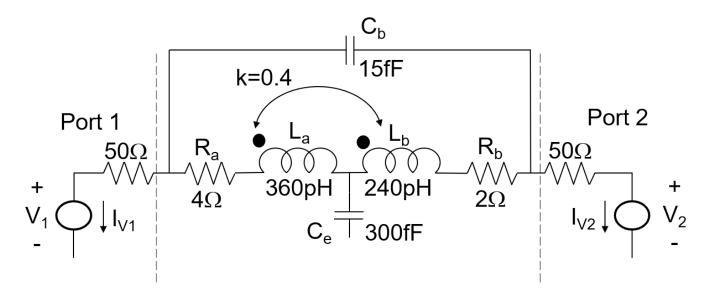

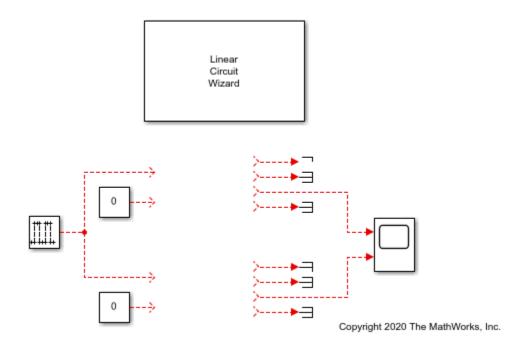

This section demonstrates how to use the Linear Circuit Wizard to obtain ss objects for detailed loop filter designs, including their device noise transfer impedances.

The Linear Circuit Wizard reads a SPICE netlist and then sets up and solves Kirchhoff%s equations algorithmically. Several different outputs are available including a report of poles, zeros, and gains. You will transform these poles, zeros, and gains into an ss object.

While this example supplies a SPICE netlist for the one loop filter that is used throughout the example, you can apply the following procedure to the SPICE netlist for any of a wide variety of circuits.

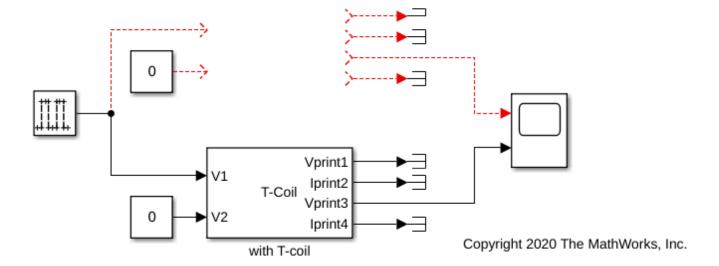

1. Open the model PllLoopDynamicsLCW.slx.

```

open system('PllLoopDynamicsLCW.slx');

```

- 2. Open the mask for the Linear Circuit Wizard.

- 3. Select the Browse function and then select the SPICE file LoopFilter.sp.

- 4. Select the Parse netlist and redefine ports function.

- 5. Go to the Port Definition tab and make sure that the desired input and output ports were configured by the netlist. If they were not configured by the netlist, you can use the Ports tab to add, delete, or modify ports.

- 6. Go to the Device noise tab and enable the device noise for any potential device noise sources you want to have modeled. In this example, enable the device noise generator for the resistors R2 and R3.

- 7. Select the Output poles and zeros function. A structure LinearCircuitWizardPoleZero is added to your workspace.

For use in the following transformations, a copy of LinearCircuitWizardPoleZero has also been saved to the file PllLCWPoleZero.mat included with this example.

The following transforms a set of poles, zeros and gains into a separate zpk model and then ss model for each transfer impedance. Note that the Gains are low frequency gains, not including poles or zeros at the origin, while the k factor is based on a different formulation of the transfer function. The gain2k function is supplied with this example to aid you in performing the gain to k transformation.

```

load('PllLCWPoleZero.mat');

p = LinearCircuitWizardPoleZero.Poles;

z = LinearCircuitWizardPoleZero.Zeros;

g = LinearCircuitWizardPoleZero.Gains;

k = gain2k(p,z,g);

[A,B,C,D] = zp2ss(z{1},p,k(1)); % Loop filter transfer impedance

zlf_lcw = ss(A,B,C,D);

[A,B,C,D] = zp2ss(z{2},p,k(2)); % R2 transfer impedance

zr2_lcw = ss(A,B,C,D);

[A,B,C,D] = zp2ss(z{3},p,k(3)); % R3 transfer impedance

zr3_lcw = ss(A,B,C,D);

```

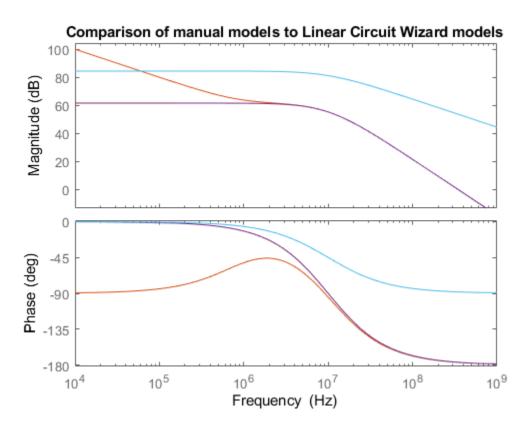

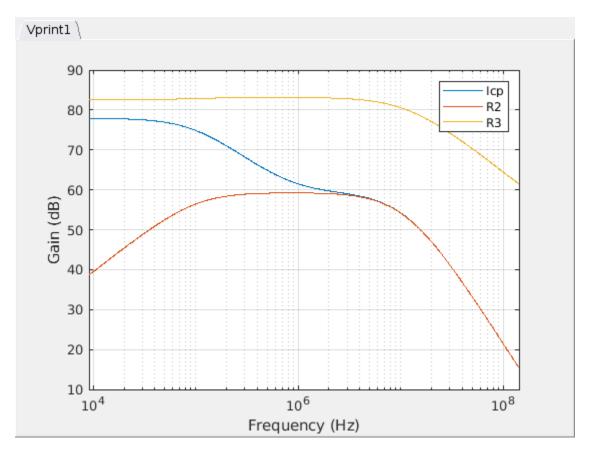

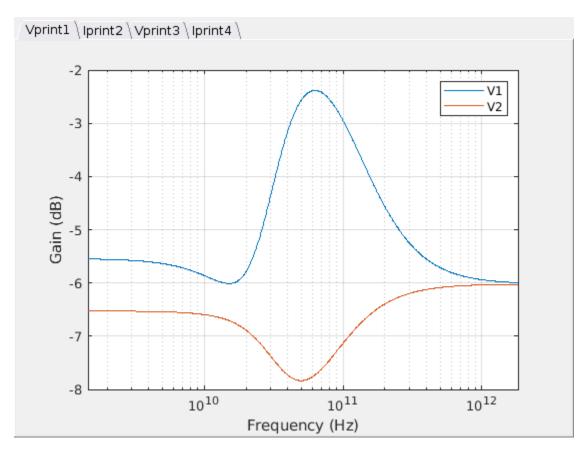

Use bode plots to demonstrate that the transfer impedance models produced through the Linear Circuit Wizard are identical to those produced through direct symbolic expressions.

figure(7)

bodeplot(zlf,zlf\_lcw,zr2,zr2\_lcw,zr3,zr3\_lcw,opts);

title('Comparison of manual models to Linear Circuit Wizard models');

#### **Z Domain Modeling**

This section presents modeling in the uniform sampled time domain (Z domain) as an alternative to modeling in the Laplace domain.

The PFD/CP only samples the phase difference between reference and output once every reference cycle [2, 3]. Thus the dynamics of the PLL are inherently tied to that uniform sample rate, and the mathematics that rigorously applies to a linear control loop analysis is Z domain mathematics. There are important behaviors such as spurious responses that occur at higher frequencies. However linear mathematics does not apply to those behaviors.

Given a Z domain expression  $Z_{LF}(z)$  of the loop filter response, the Z domain expression for the loop gain [3] is

$$G(s) = \frac{\tau_{ref}I_{CP}K_{VCO}}{1 - z^{-1}}Z_{LF}(z)$$

The remaining task is to convert the  $Z_{LF}(s)$  function from the Laplace domain analysis to the Z domain. There are many ways to perform this task, and several of them have been implemented in the MATLAB c2d function. The appropriate option in this application is zero-order hold, the default for the c2d function. Note that the Z domain modeling does require an explicit sample time value equal to the period of the reference signal.

```

fref = 30e6;

ts = 1/fref;

vcoz = ss(1,ts*PllKphi*PllKvco,1,0,ts);

divNz = ss(0,0,0,1/PllN,ts);

zlfz = c2d(zlf,ts);

Gz = vcoz*zlfz;

Hz = feedback(Gz, divNz);

Hz.InputName = 'ref';

Hz.OutputName = 'out';

GzoverN = Gz*divNz;

```

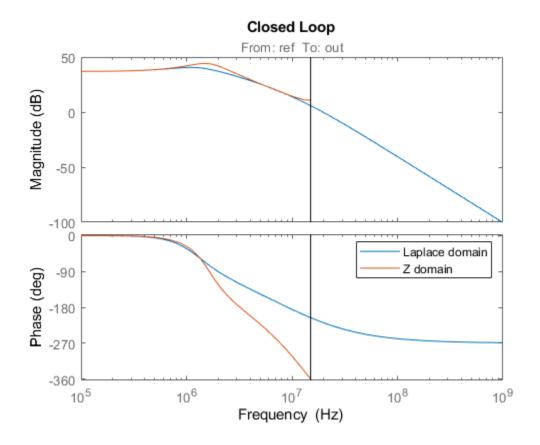

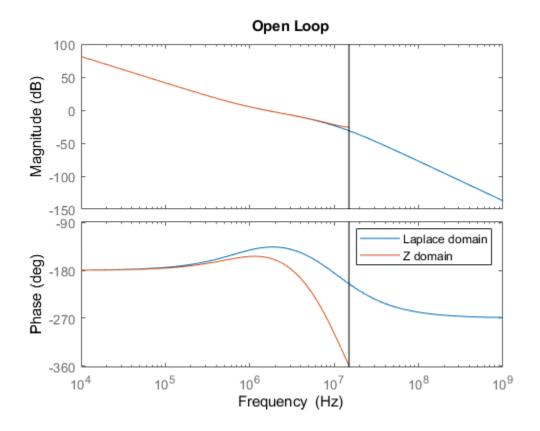

## Compare Z domain with Laplace domain

It is informative to compare the Z domain predictions of the closed loop, open loop, and step responses with the corresponding results from the Laplace domain analysis.

```

figure(1);

bodeplot(H,Hz,opts);

title('Closed Loop');

legend('Laplace domain','Z domain');

figure(2);

bodeplot(GoverN,GzoverN,opts);

title('Open Loop');

legend('Laplace domain','Z domain');

figure(3);

step(H,Hz);

title('Lock Time');

legend('Laplace domain','Z domain');

```

In this comparison, note that while the frequency response and step response from the Z domain analysis are very similar to those obtained from the Laplace domain analysis, the phase margin predicted by the Z domain analysis is far less than the design value chosen as part of the design in the Laplace domain. This is a critical observation, as the loop phase margin is a fundamental requirement of the control loop design.

As stated in [2], this is a typical result for PLLs whose loop bandwidth equals or exceeds one tenth of the reference frequency. For much smaller loop bandwidths the difference between Z domain and Laplace domain is much smaller.

Note, however, that it is the Laplace domain analysis result that closely matches the time domain simulation. You might find this to be a suitable topic for further study.

## **Advantages and Disadvantages of Phase Domain Modeling**

- + Both open and closed loop linear control analyses are easy, fast, reliable and accurate.

- + You can readily include detailed phase noise modeling in your analysis, with the effect of each phase noise source indicated clearly and accurately.

- + Using the Linear Circuit Wizard, you can easily and accurately include detailed linear circuit designs, especially for the loop filter.

- Phase domain modeling is limited to one sample per reference cycle, and therefore a Nyquist frequency limit of one half the reference frequency. For example, it is not applicable to the analysis of spurious output responses past this Nyquist limit.

- While phase domain modeling can be applied to nonlinear behaviors such as frequency acquisition, such applications lose the inherent advantages of linear control analysis associated with phase domain modeling.

- Phase domain modeling is usually not applicable to models that combine the PLL with other circuits that use the output of the PLL.

#### References

- 1. Dean Banerjee, PLL Performance, Simulation and Design, 5th edition, Texas Instruments, SNAA106C, May 2017.

- 2. P. K. Hanumolu, M. Brownlee, K. Mayaram and Un-Ku Moon, "Analysis of charge-pump phase-locked loops," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 51, no. 9, pp. 1665-1674, Sept. 2004, doi: 10.1109/TCSI.2004.834516.

- 3. Mike Steinberger, "Discrete Time Modeling of PLLs", MathWorks document, May 31, 2022.

# **DC Featured Examples**

- "Effect of Metastability Impairment in Flash ADC" on page 2-2

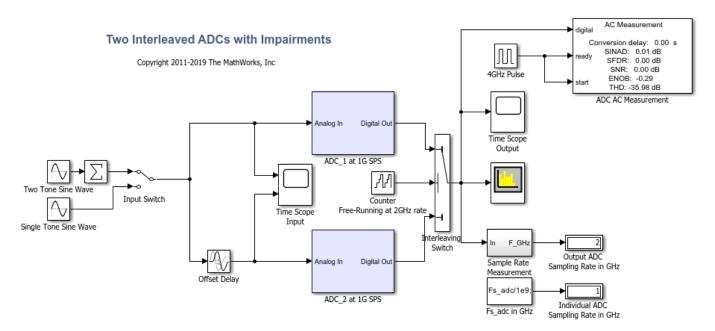

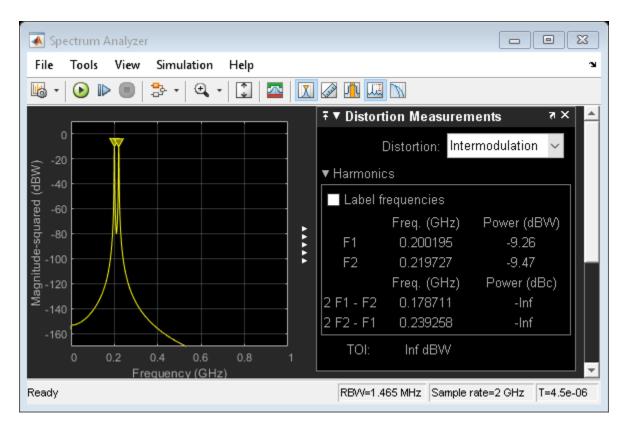

- "Design and Evaluate Interleaved ADC" on page 2-8

- "Design and Evaluate Successive Approximation ADC Using Stateflow" on page 2-19

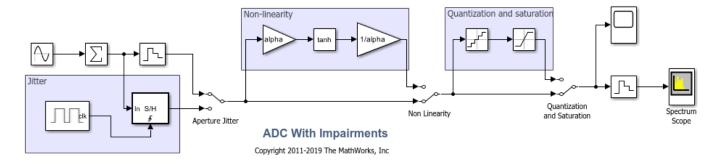

- "Analyzing Simple ADC with Impairments" on page 2-27

- "Subranging ADC" on page 2-35

- "Measuring Offset and Gain Errors in ADC" on page 2-44

- "Compare SAR ADC to Ideal ADC" on page 2-48

- "ADC Linearity Measurement Using Histogram" on page 2-52

- "Oversampling Interpolating DAC" on page 2-64

- "Design and Evaluate Segmented DAC" on page 2-73

- "Compare Binary Weighted DAC to Ideal DAC" on page 2-78

- "Delta Sigma Modulator Data Converter with Half-Band Filter for Decimation" on page 2-81

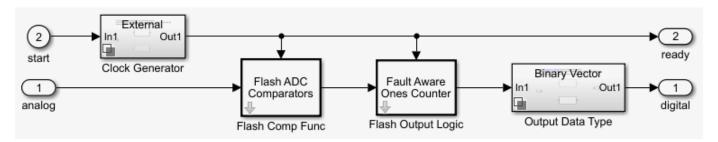

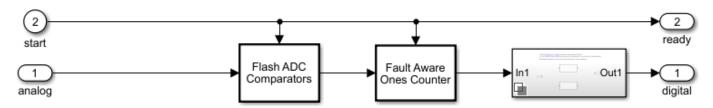

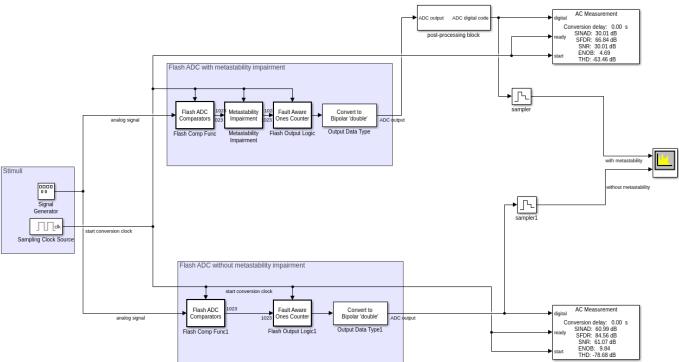

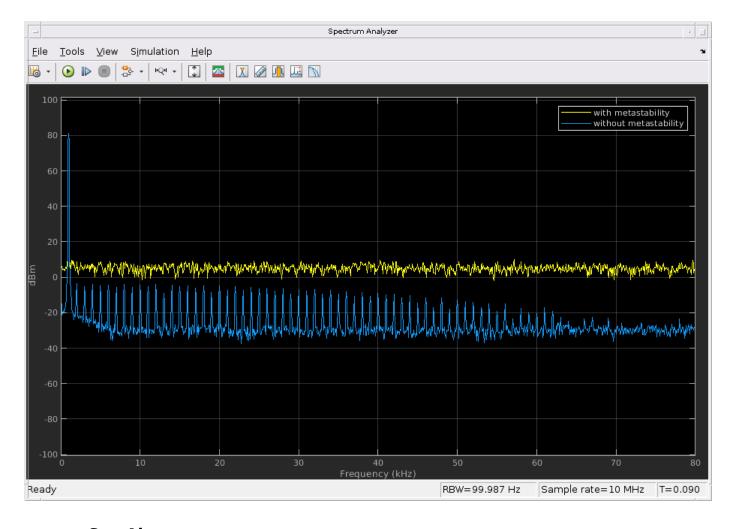

## Effect of Metastability Impairment in Flash ADC

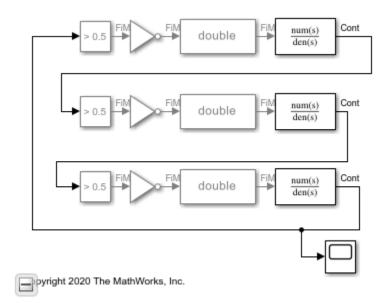

This example shows how to customize a flash Analog to Digital Converter (ADC) by adding the metastability probability as an impairment. You can measure the metastability probability impairment to validate your implementation. The example also shows the effect of metastability on the dynamic performance of the flash ADC. When the digital output from a comparator is ambiguous (neither zero nor one), the output is defined as metastable. The ambiguous output is expressed as NaN. This example model uses a MATLAB function block to add the metastability impairment to a flash ADC architecture. Another subsystem reports the metastability probability on the fly.

#### **Customize Flash ADC**

Extract the inner structure of the flash ADC to add customized impairment. Add a Flash ADC block from the Mixed-Signal Blockset<sup> $\mathsf{TM}$ </sup> library to a Simulink® canvas. Look under the mask to find the flat structure of the ADC. Copy and paste the complete structure to another new blank canvas.

Delete the Clock Generator block because it is not used to provide the start conversion clock. An external Stimuli subsystem is used for that purpose. The flash ADC now consists of three major components:

- Flash ADC Comparators

- Fault Aware Ones Counter

- Output Data Type

#### **Flash ADC Comparators**

An N-bit flash ADC uses  $2^{Nbits}$  comparators in parallel. The Flash ADC Comparators subsystem itself is based on MATLAB® code. Before the simulation starts, the comparators calculate the individual reference voltages and store them in a vector. On every specified edge, the input is compared to the references using MATLAB's ability to compare vectors. This generates thermometer code similar to the real flash ADC, without the lag from N individual comparator blocks in the model.

To create a 10- bit ADC, set **Number of bits (nbits)** to 10, **Input Range** to [-1 1], and **INL Vector** to 0. **Trigger type** is kept at its default value Rising edge.

#### **Fault Aware Ones Counter**

The Fault Aware Ones Counter subsystem implements the impairments in the flash ADC architecture. Real ADCs handle conversion from thermometer to binary through logic circuits. This subsystem takes the sum-of-elements of the vector stored by the comparators and applies that sum to a lookup table to simulate missing codes, otherwise known as bubbles.

Set the Fault Aware Ones Counter parameters: **Number of Bits (nbits)** to 10, **Input Range** to [-1 1], and **Bubble Codes** to []. **Trigger type** is kept at its default value Rising edge.

#### **Output Data Type**

The Output Data Type subsystem handles conversion from the data type at the output of the Fault Aware Ones Counter to the data type specified on the mask of the Flash ADC.

Break the library link between the Output Data Type block and its reference library. Set **Input dynamic range** to [-1 1] and **Bipolar data type** to double.

#### Implement Metastability Probability as an Impairment to Flash ADC

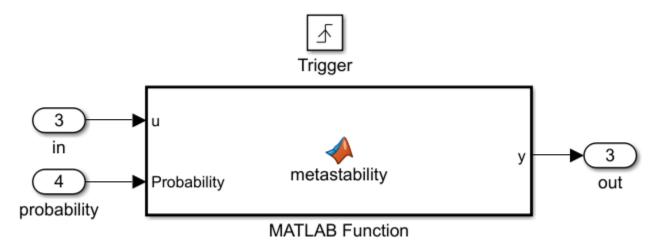

To add metastability impairment, place a triggered subsystem with a MATLAB function block after the Flash ADC Comparators subsystem. The MATLAB function block sets thermometer code signals to NaNs with a probability from a uniform random number generator. The block resets the signals on the next relevant edge which is why a triggered subsystem is used. Use this code to implement the Metastability Impairment subsystem.

```

% function y = metastability(u, Probability)

% mult = ones(size(u));

% mult(rand(size(u)) < Probability(1)) = NaN; % metastability = NaN

% y = u .* mult;

% end</pre>

```

Provide the metastability probability that you want to implement through a constant block connected to the **Probability** port.

#### **Implement Measuring Metastability Probability**

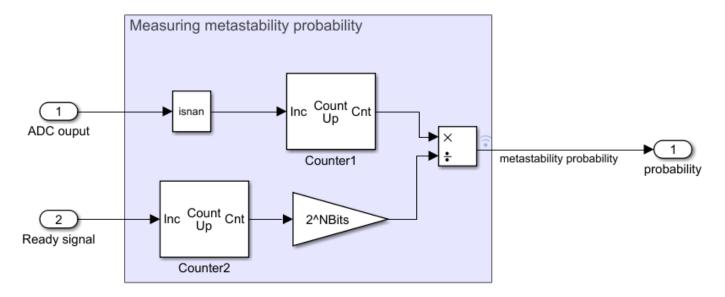

To measure metastability impairment, count the number of NaNs encountered and divide that by the number of total comparator outputs generated during the complete simulation. A simple Simulink implementation of metastability probability measurement is:

The Inports are:

- ADC output- Receives the output digital code generated by the flash ADC.

- Ready signal- Receives the ready signal which represents the rate at which the digital conversion is taking place. The digital code gets generated at each rising edge of the signals received by 'Ready signal' port.

#### **Simulation for Metastability Measurement**

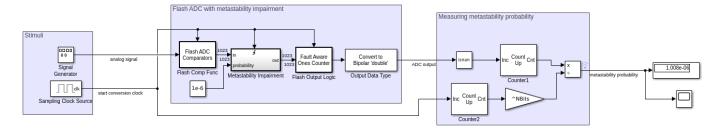

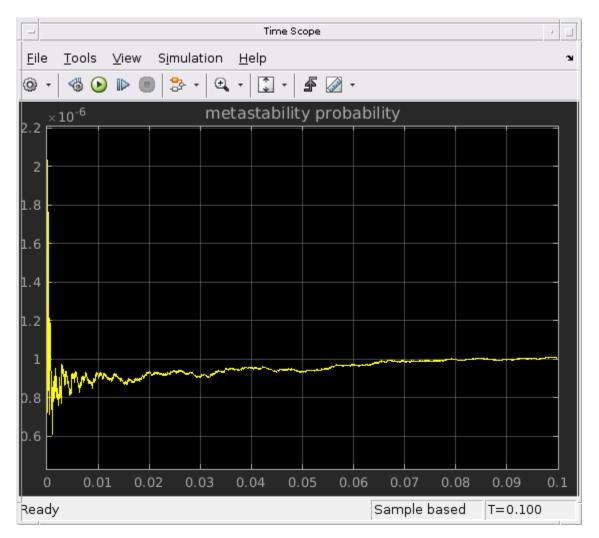

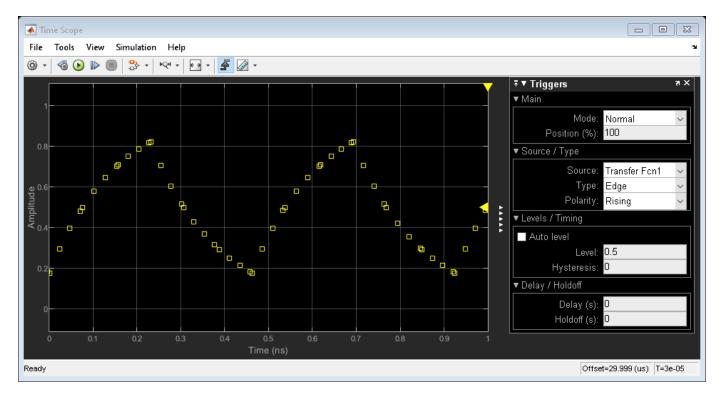

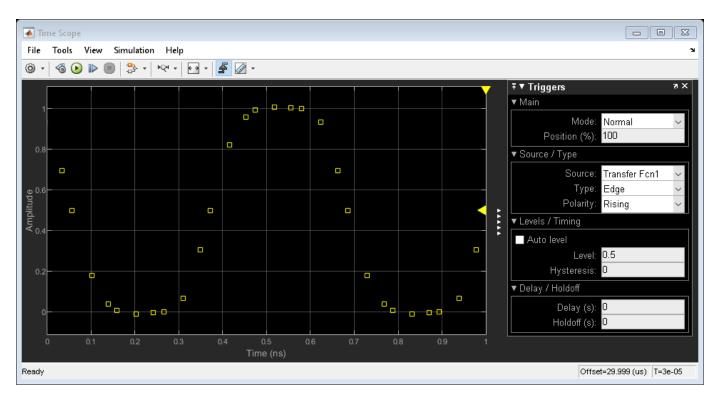

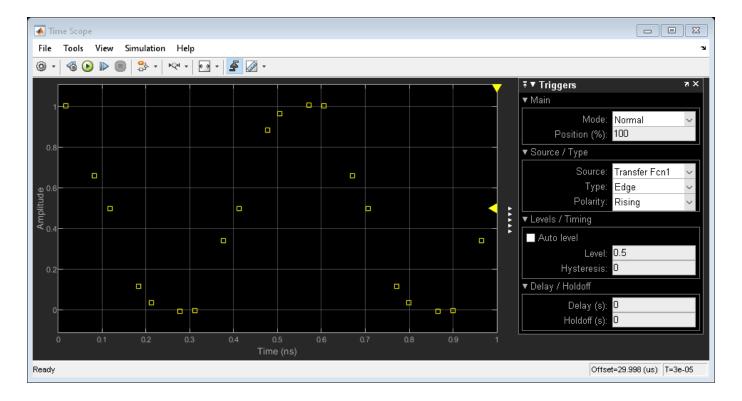

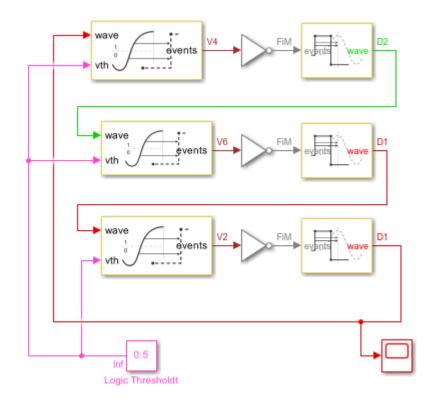

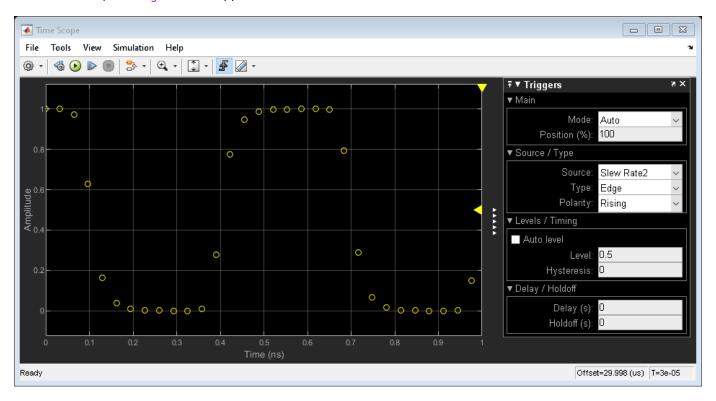

The model below combines the customized flash ADC with its output connected to the metastability probability measurement system. In the model, you have a 10-bit flash ADC with metastability probability of 1e-6 added. The Stimuli subsystem generates an analog signal of 100 Hz and a start conversion clock with a frequency of 100 MHz. The ADC operates at the rate defined by the start conversion clock frequency. A dashboard scope provides the behavior of the probability number over time. A display block shows the current probability being measured by the subsystem. You must run the simulation for a long enough period to see the probability number settled at the desired value, in this case 1e-6.

```

NBits=10;

model1='flashAdc_metastability.slx';

open_system(model1);

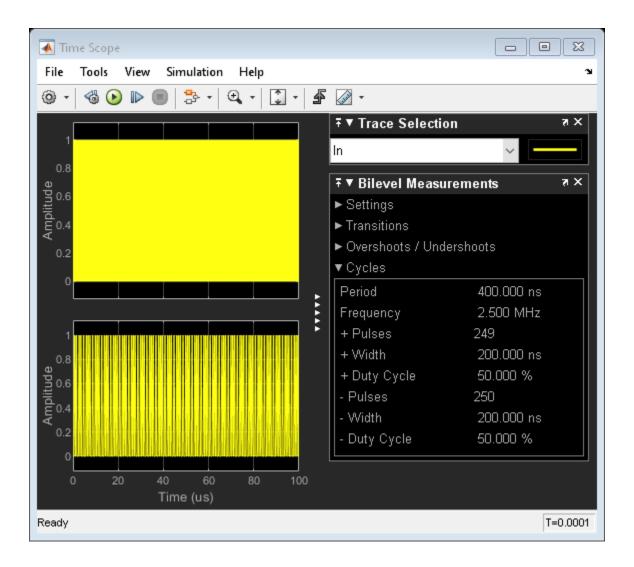

open_system([bdroot,'/Time Scope']);

sim(model1);

```

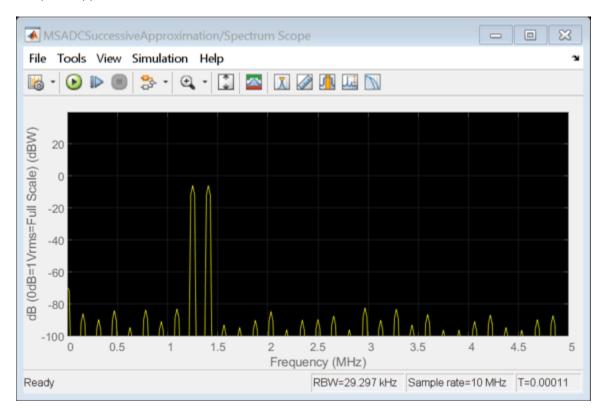

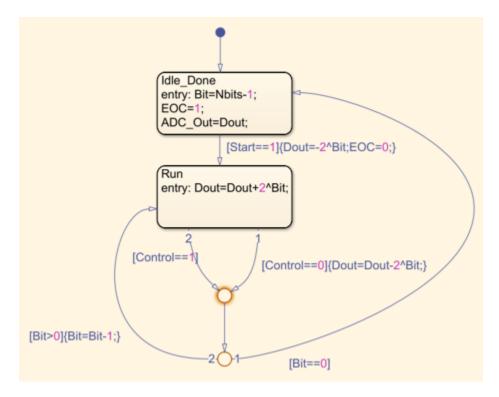

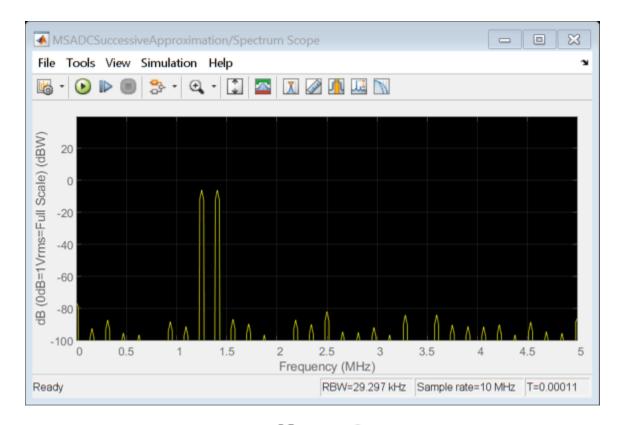

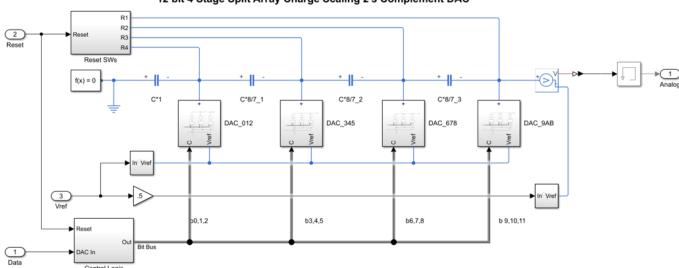

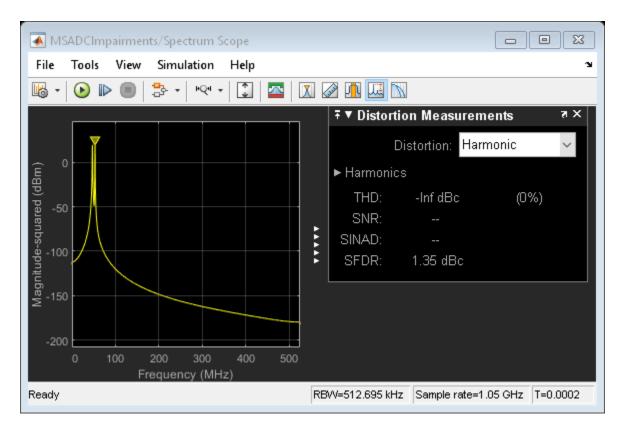

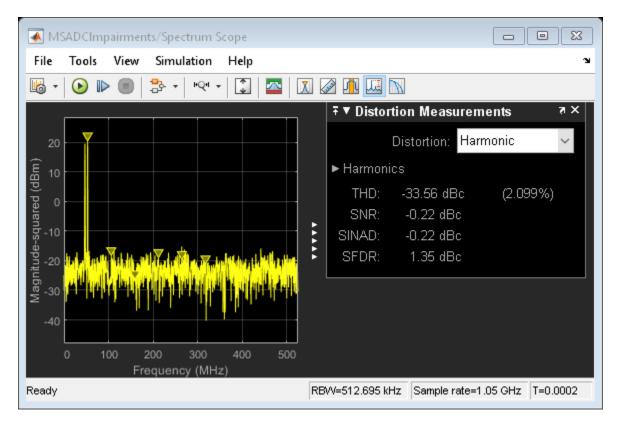

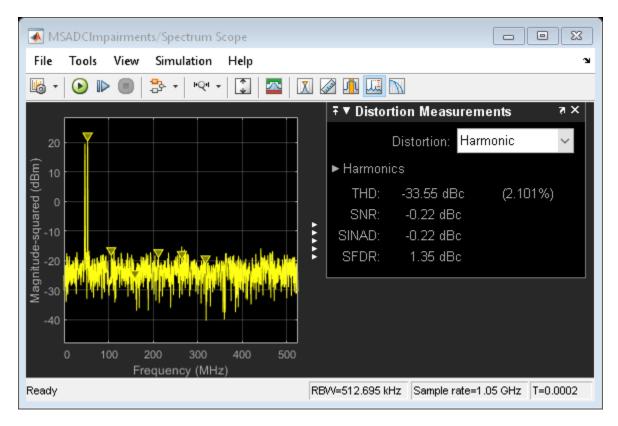

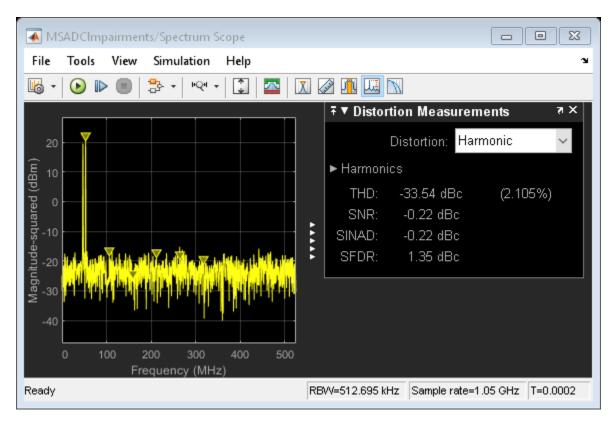

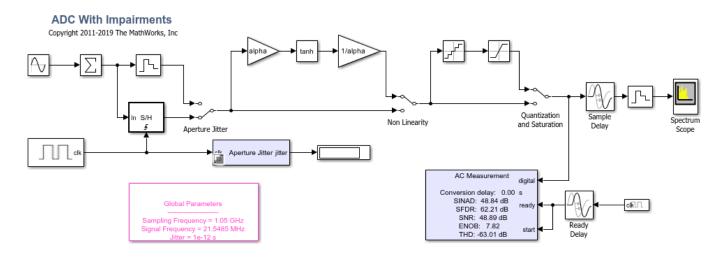

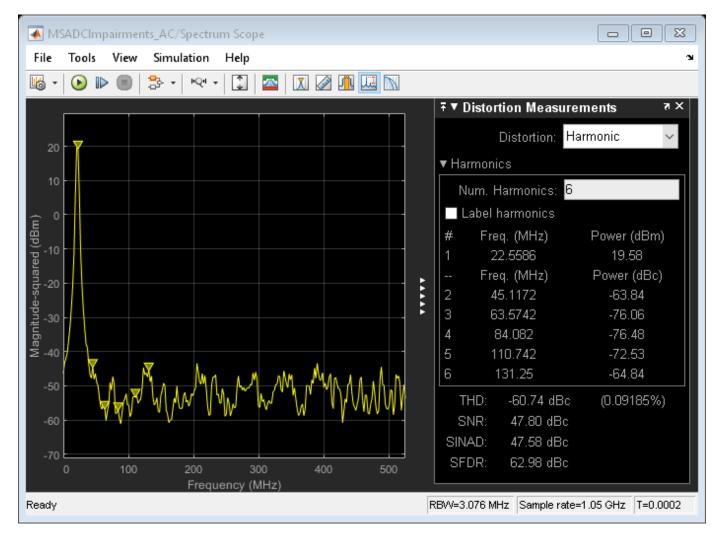

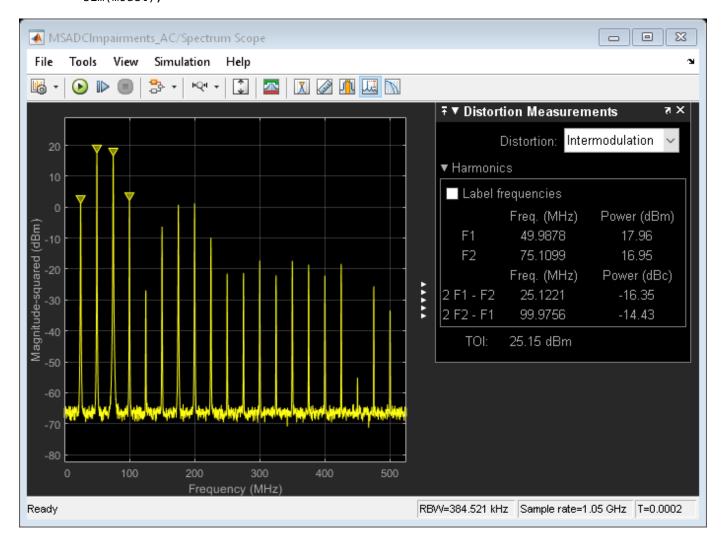

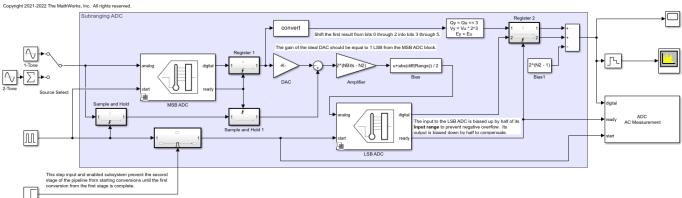

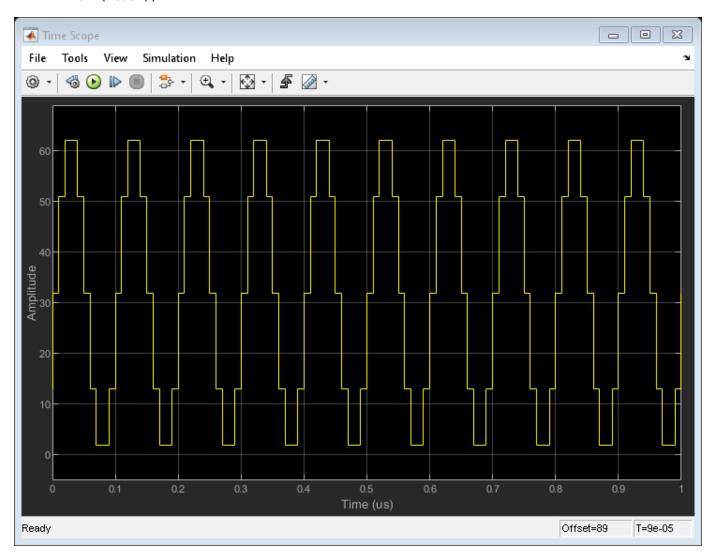

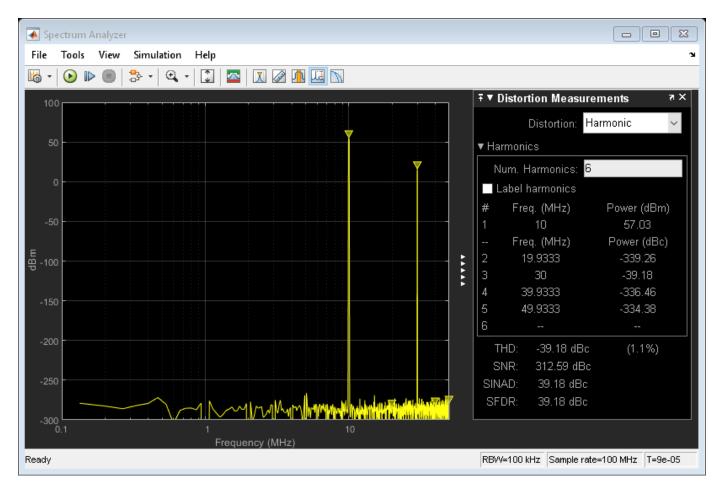

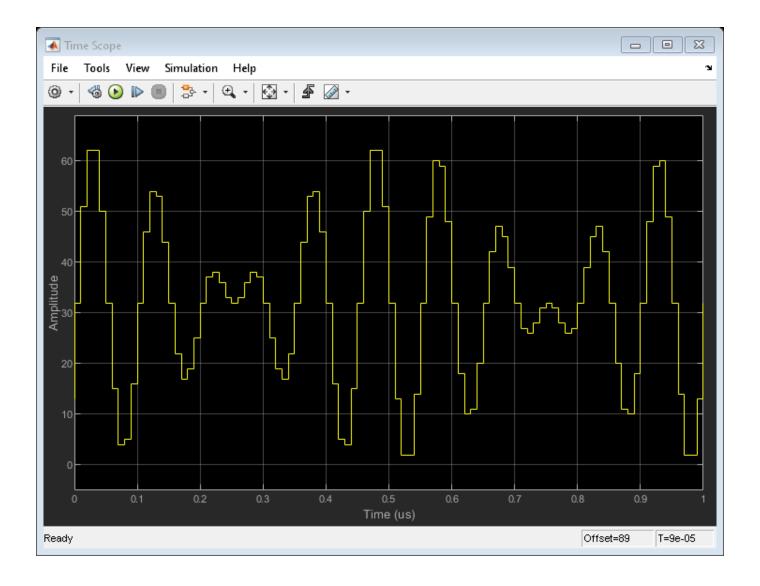

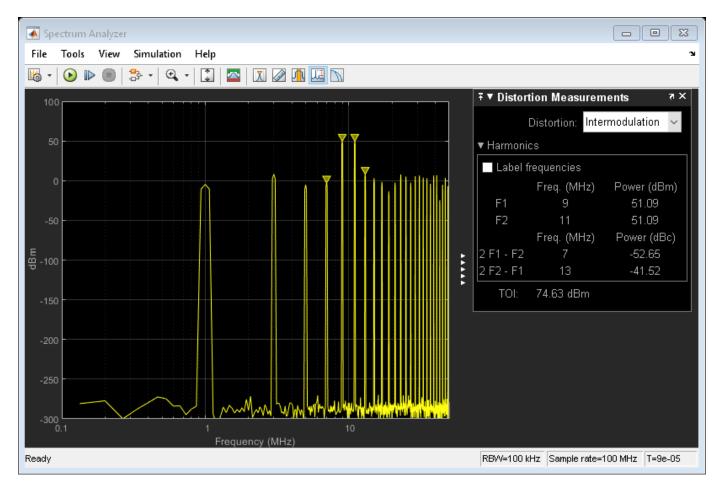

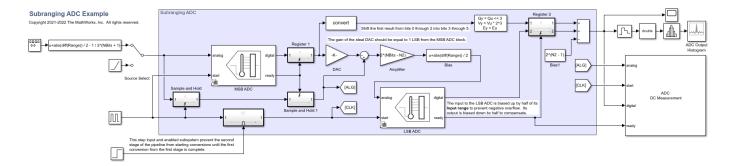

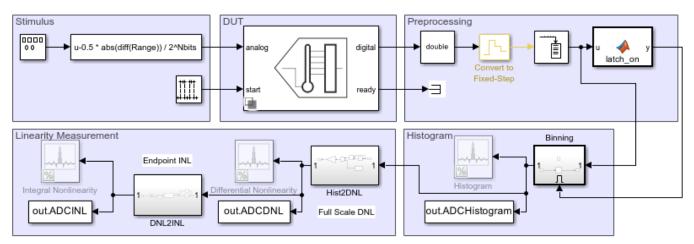

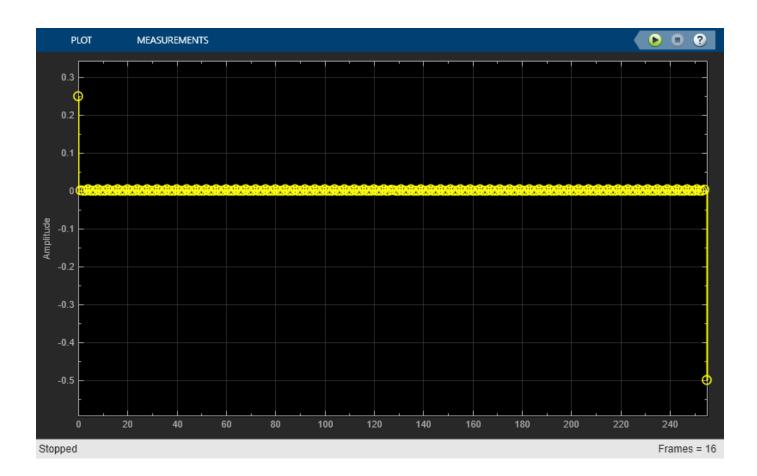

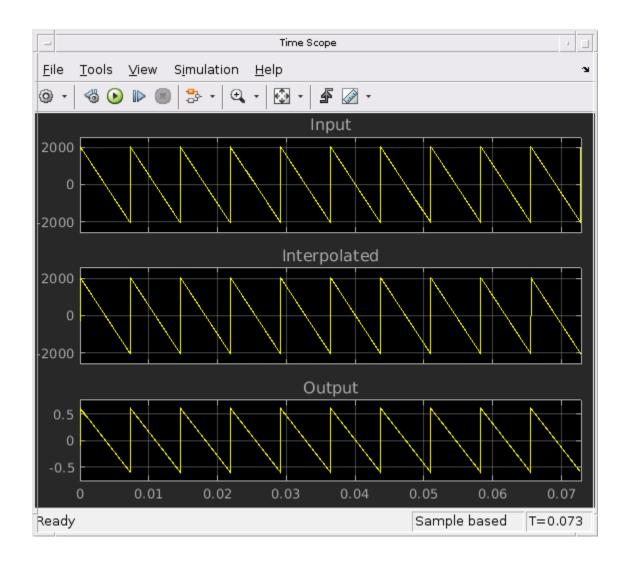

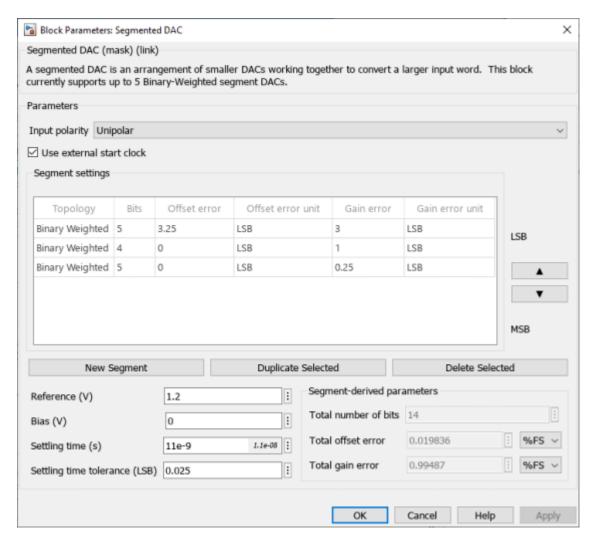

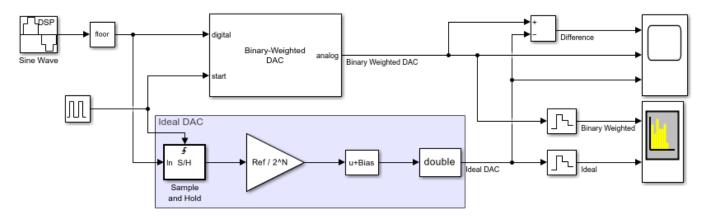

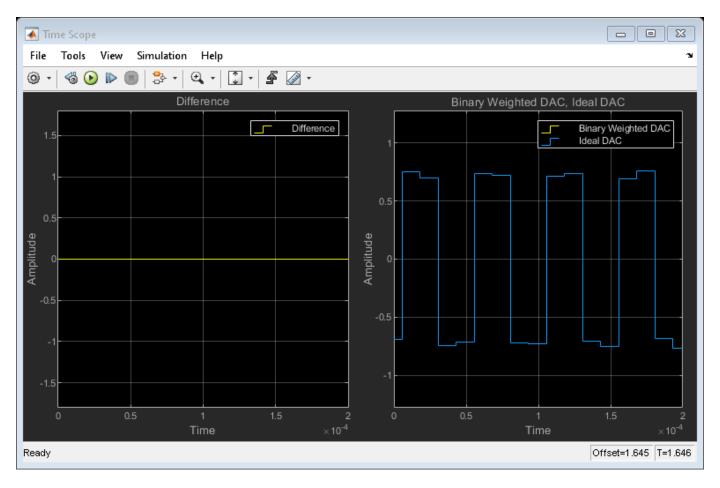

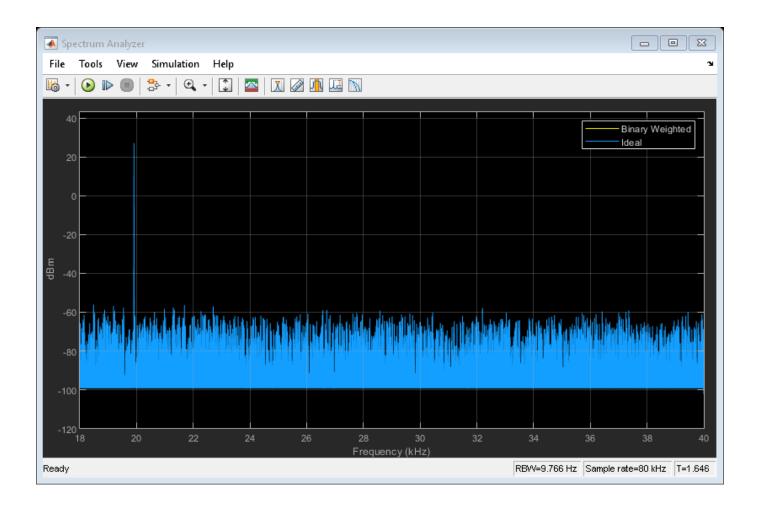

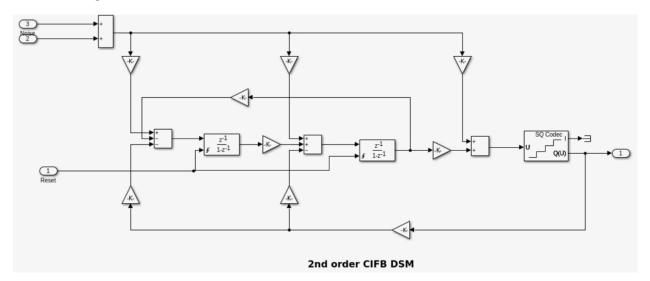

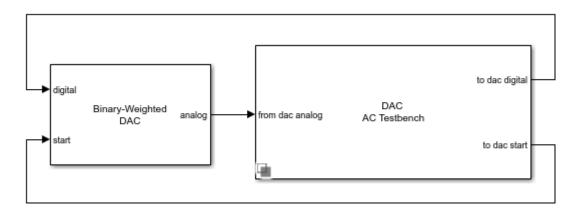

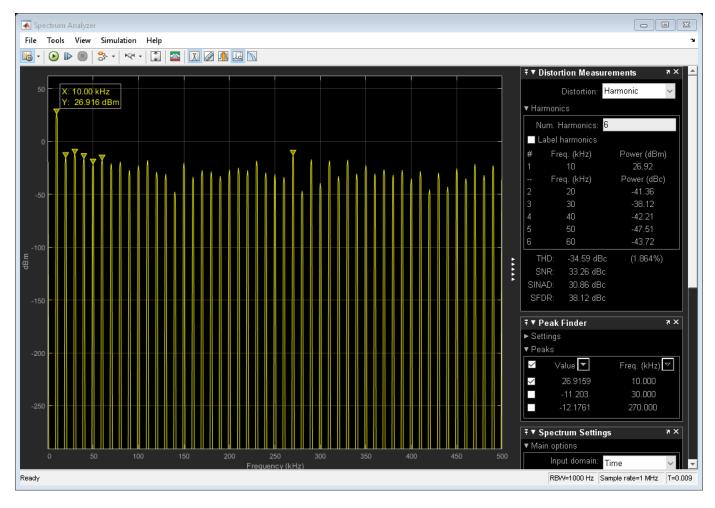

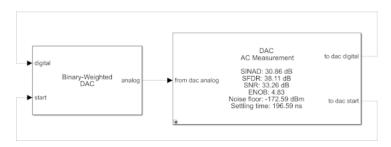

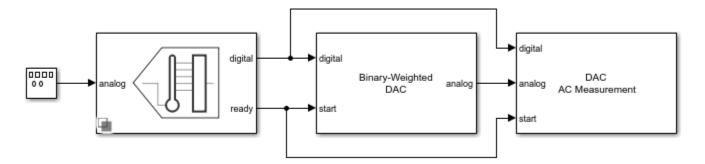

#### Effect of Metastability on Dynamic Performance of ADC